# Integrated Circuit Fabrication Laboratory

*Final Report – Group 2*

**Group members:**

Fengyuan Lai

Tyler Mason

Dibyajoyti Mohanty

Omotoyosi Taiwo

Seth Lowenstern

**Under the guidance of:**

Prof. T. Paul Chow

Peng-Yu Su

Bryant Colwill

Kent Way

## Contents

|                                                         |    |

|---------------------------------------------------------|----|

| Acknowledgment .....                                    | 15 |

| Abstract .....                                          | 16 |

| Team Responsibility .....                               | 17 |

| 1. Technical Background .....                           | 19 |

| 1.1 Introduction .....                                  | 19 |

| 1.2 Device Physics .....                                | 20 |

| 1.2.1 Introduction to MOSFET .....                      | 20 |

| 1.2.2 Different Types of Field-Effect Transistors ..... | 21 |

| 1.2.3 Basic Device Characteristics .....                | 21 |

| 1.2.4 MOS Structure.....                                | 21 |

| 1.2.5 Current-Voltage Characteristics.....              | 29 |

| 1.2.6 Non-ideal MOSFET .....                            | 33 |

| 1.2.7 Additional Effects in MOSFETs .....               | 33 |

| 1.3 Basic Processing Steps for MOSFETs .....            | 36 |

| 1.3.1 Wafer Cleaning: .....                             | 37 |

| 1.3.2 Thermal oxidation: .....                          | 38 |

| 1.3.3 Photolithography .....                            | 40 |

| 1.3.4 Material deposition.....                          | 43 |

| 1.3.5 Etching .....                                     | 46 |

| 1.3.6 Ion implantation .....                            | 47 |

| 1.3.7 Diffusion.....                                    | 48 |

| 1.3.8 Interconnections and contacts .....               | 49 |

| 1.4 Process Modeling .....                              | 51 |

| 1.4.1 NMOS Process Simulation.....                      | 51 |

| 1.4.2 PMOS Process Simulation: .....                    | 65 |

| 1.5 Characterization and Testing.....                   | 79 |

|       |                                                                            |     |

|-------|----------------------------------------------------------------------------|-----|

| 1.5.1 | Electrical Contact Measurements .....                                      | 79  |

| 1.5.2 | Sheet Resistance Measurement: Van der Pauw (VdP) Method .....              | 81  |

| 1.5.3 | C-V Measurements.....                                                      | 83  |

| 1.5.4 | I-V Characteristics.....                                                   | 84  |

| 2.    | Detailed Processing Procedures .....                                       | 87  |

| 2.1   | Week 1. Field Oxide Growth .....                                           | 87  |

| 2.1.1 | Wafer Scribing .....                                                       | 87  |

| 2.1.2 | RCA Clean for Wafers .....                                                 | 87  |

| 2.1.3 | Field Oxide Growth.....                                                    | 90  |

| 2.2   | Week 2. Active Area Patterning.....                                        | 91  |

| 2.2.1 | Oxide Thickness Measurement .....                                          | 91  |

| 2.2.2 | Photolithography for Active Area Patterning.....                           | 93  |

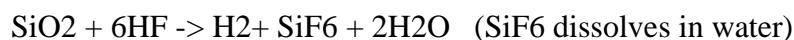

| 2.2.3 | Field Oxide Etching .....                                                  | 95  |

| 2.3   | Week 3. Gate Oxide Growth and Poly-Si Deposition.....                      | 96  |

| 2.3.1 | RCA Clean for Wafers .....                                                 | 96  |

| 2.3.2 | Gate Oxide Growth .....                                                    | 96  |

| 2.3.3 | Poly-Si Deposition .....                                                   | 97  |

| 2.4   | Week 4. Source and Drain Patterning .....                                  | 98  |

| 2.4.1 | Gate Oxide Measurement.....                                                | 98  |

| 2.4.2 | Photolithography for Source/Drain Patterning.....                          | 98  |

| 2.4.3 | Reactive Ion Etching .....                                                 | 99  |

| 2.4.4 | Ion Implantation .....                                                     | 100 |

| 2.5   | Week 5. Deposition and Densification of Inter-Level Dielectric (ILD) ..... | 100 |

| 2.5.1 | Caro's Etch and BOE .....                                                  | 100 |

| 2.5.2 | ILD Deposition.....                                                        | 100 |

| 2.5.3 | ILD Densification.....                                                     | 102 |

| 2.6   | Week 6. ILD Patterning for Metal Contacts .....                            | 103 |

|       |                                                        |     |

|-------|--------------------------------------------------------|-----|

| 2.6.1 | Thickness Measurement of ILD after Densification ..... | 103 |

| 2.6.2 | Photolithography for ILD Patterning .....              | 103 |

| 2.6.3 | ILD Etching.....                                       | 103 |

| 2.6.4 | Post RIE etch and Photoresist Stripping .....          | 105 |

| 2.7   | Week 7. Metallization .....                            | 105 |

| 2.7.1 | Native Oxide Etch .....                                | 105 |

| 2.7.2 | Aluminum Sputtering.....                               | 105 |

| 2.7.3 | Aluminum Patterning .....                              | 106 |

| 2.7.4 | Aluminum Etch .....                                    | 107 |

| 2.8   | Week 8. Backside Metal Contact .....                   | 107 |

| 3.    | Electrical Testing .....                               | 110 |

| 3.1   | Contact Measurements .....                             | 110 |

| 3.1.1 | Transmission Line: .....                               | 110 |

| 3.1.2 | Kelvin Structure: .....                                | 111 |

|       | Contact resistance (Ohm).....                          | 112 |

|       | Contact resistivity (Ohm-cm <sup>2</sup> ).....        | 112 |

|       | Standard deviation among wafers.....                   | 112 |

|       | nMOS 4x4.....                                          | 112 |

| 44.41 | 112                                                    |     |

|       | 7.0*10 <sup>-6</sup> .....                             | 112 |

| 1.19  | 112                                                    |     |

|       | nMOS 8x8.....                                          | 112 |

| 22.63 | 112                                                    |     |

|       | 1.5*10 <sup>-5</sup> .....                             | 112 |

| 0.15  | 112                                                    |     |

|       | nMOS 16x16.....                                        | 112 |

| 9.6   | 112                                                    |     |

|                                      |     |

|--------------------------------------|-----|

| 2.5*10^-5 .....                      | 112 |

| 0.04 112                             |     |

| pMOS 4x4.....                        | 113 |

| 34.77 113                            |     |

| 5.6*10^-6 .....                      | 113 |

| -- 113                               |     |

| pMOS 8x8.....                        | 113 |

| 24.39 113                            |     |

| 1.6*10^-5 .....                      | 113 |

| -- 113                               |     |

| pMOS 16x16.....                      | 113 |

| 11.97 113                            |     |

| 3.0*10^-5 .....                      | 113 |

| -- 113                               |     |

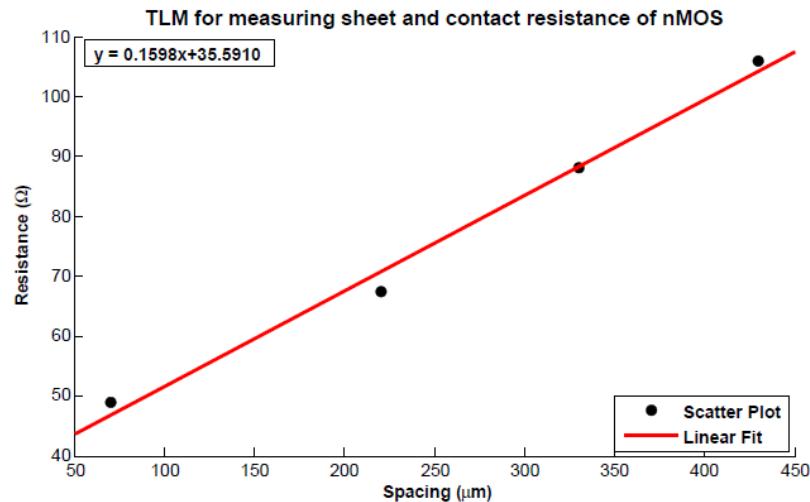

| 3.2 Sheet Resistance.....            | 113 |

| Wafer.....                           | 114 |

| Avg Resistance.....                  | 114 |

| Sheet Resistance (Ohm/square) .....  | 114 |

| Standard deviation among wafers..... | 114 |

| nMOS.....                            | 114 |

| 8.26 114                             |     |

| 37.1 114                             |     |

| 1.4 114                              |     |

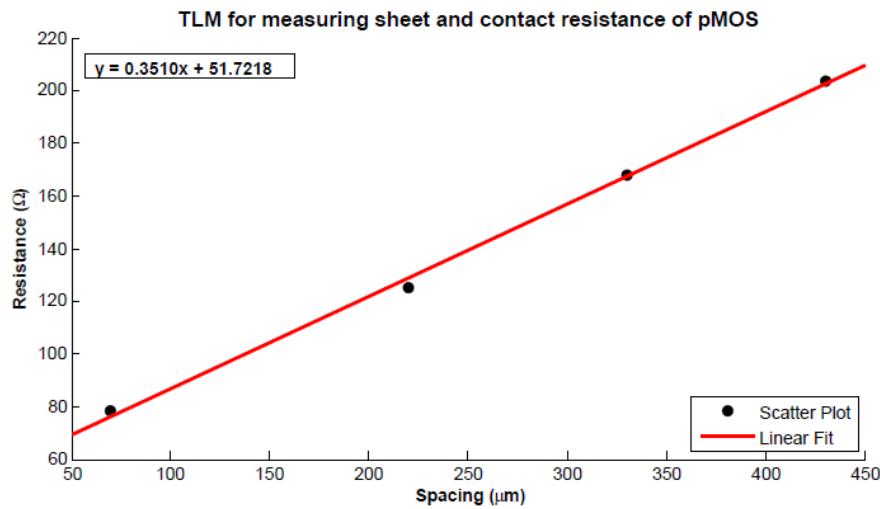

| pMOS.....                            | 114 |

| 29.5 114                             |     |

| 133.4 114                            |     |

| -- 114                               |     |

|       |                                        |     |

|-------|----------------------------------------|-----|

| 3.3   | NMOS IV Characterization.....          | 114 |

| 3.3.1 | Parallel Resistance.....               | 115 |

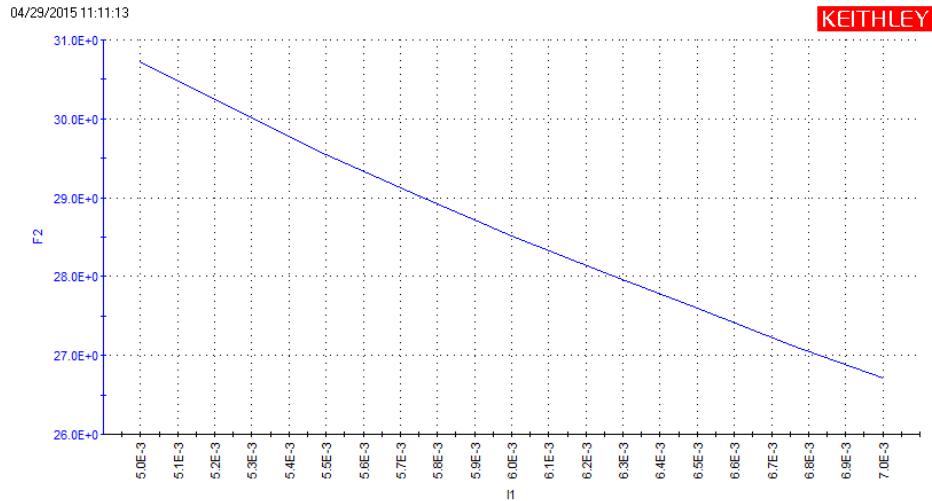

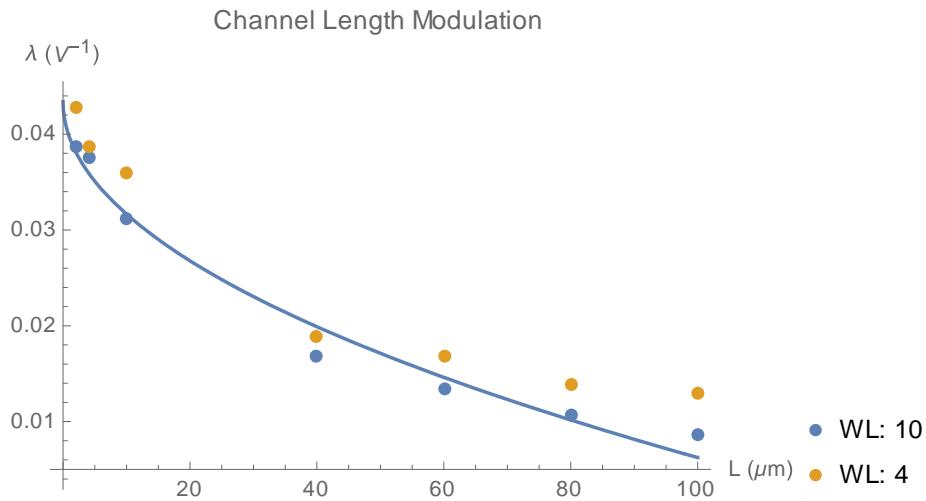

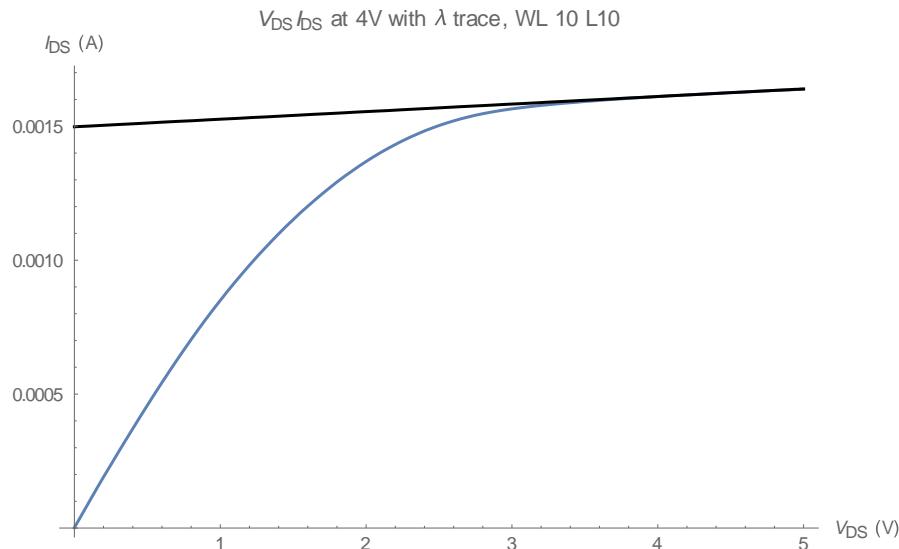

| 3.3.2 | Channel Length Modulation.....         | 117 |

| 3.3.3 | $V_T$ Extraction.....                  | 118 |

| 3.3.4 | $\mu_n$ and $C_{ox}$ .....             | 119 |

| 3.3.5 | Table of Extracted Values .....        | 119 |

| 3.4   | PMOS IV Characterization .....         | 120 |

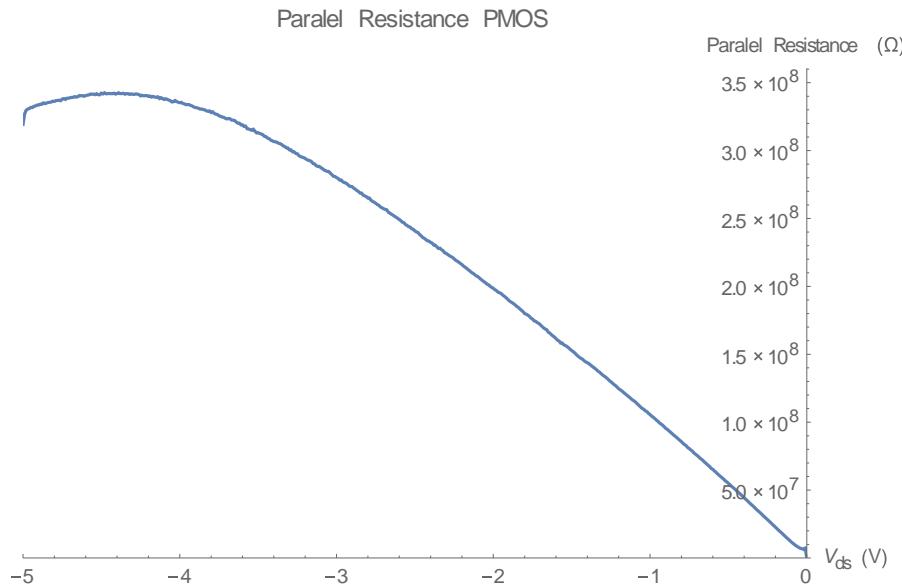

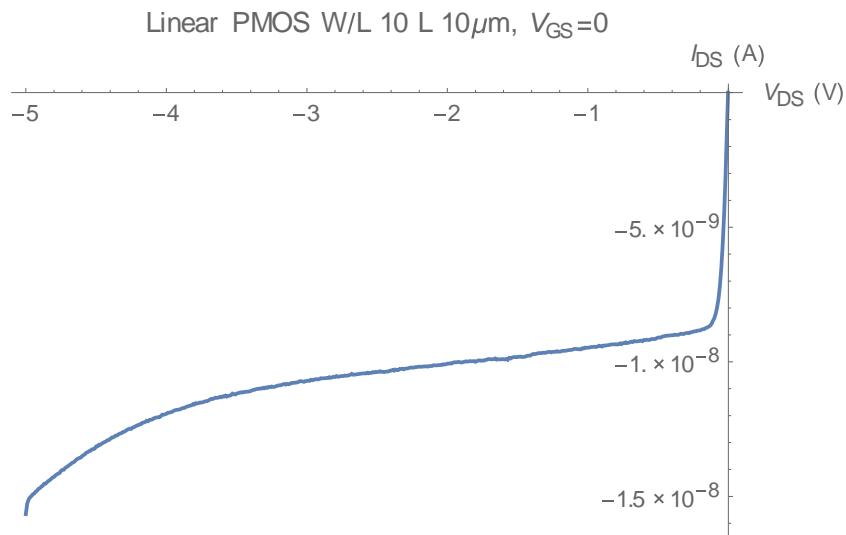

| 3.4.1 | Parallel Resistance.....               | 121 |

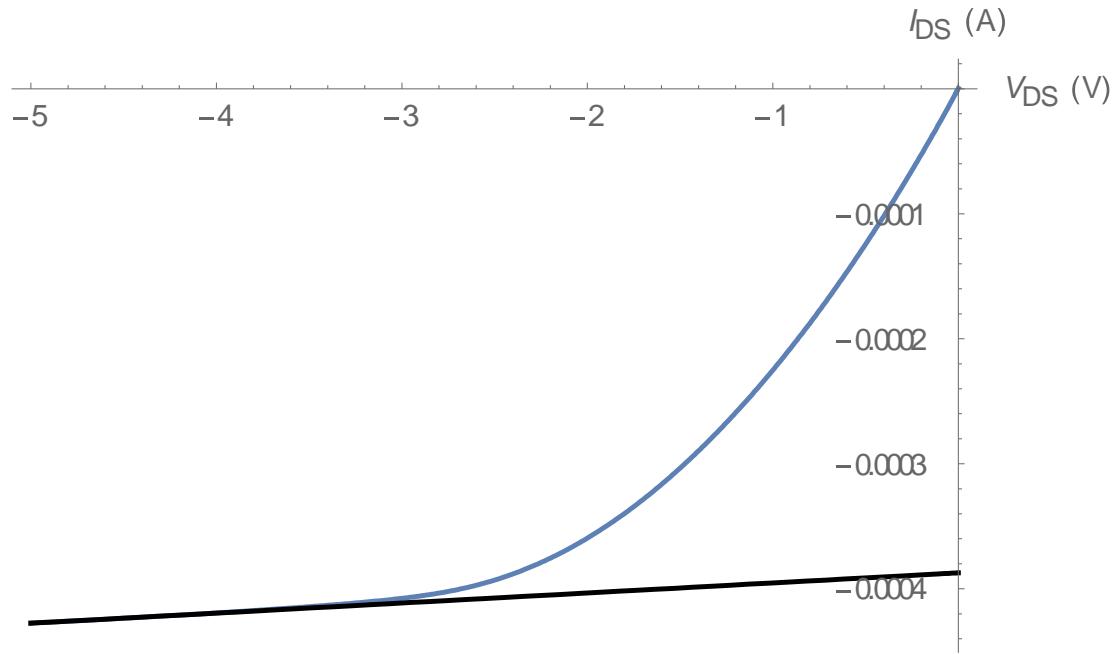

| 3.4.2 | Channel Length Modulation.....         | 122 |

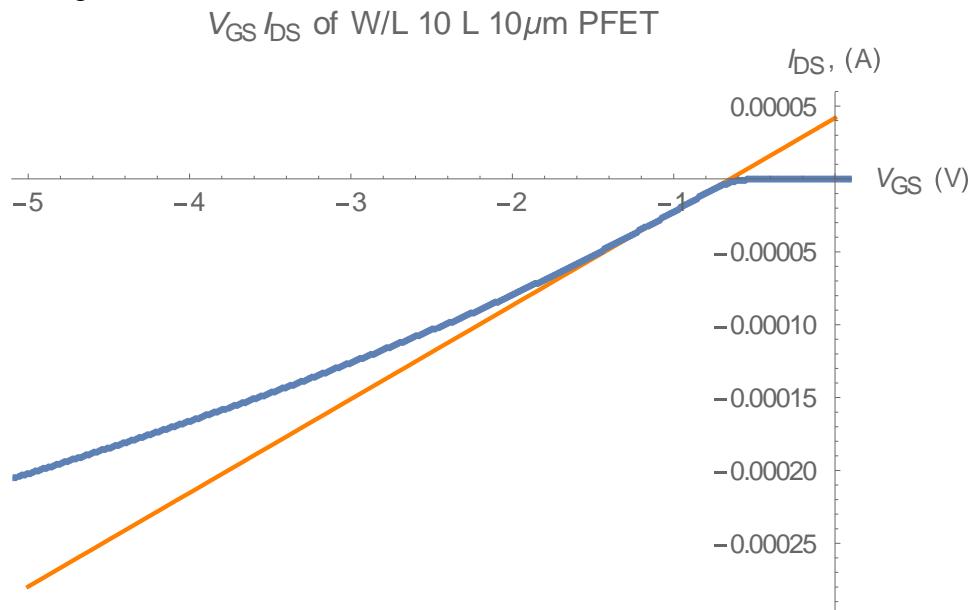

| 3.4.3 | $V_T$ Extraction.....                  | 123 |

| 3.4.4 | $\mu_p$ and $C_{ox}$ .....             | 124 |

| 3.4.5 | Table of Extracted Values .....        | 124 |

| 3.5   | Device Modeling .....                  | 124 |

| 3.6   | Transconductance.....                  | 126 |

| 3.7   | Capacitance-Voltage Measurements ..... | 127 |

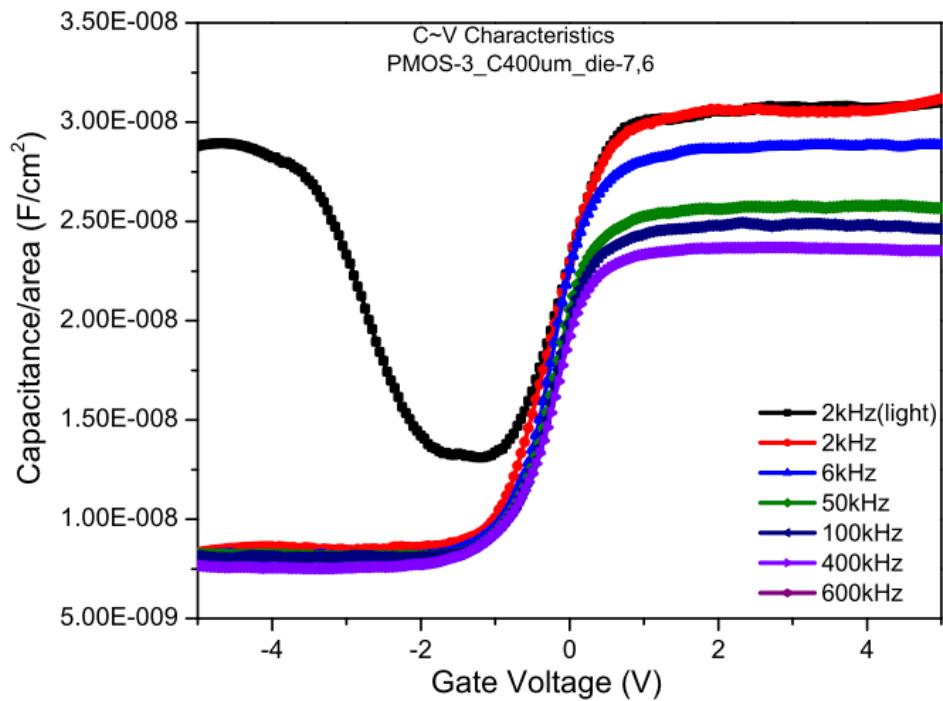

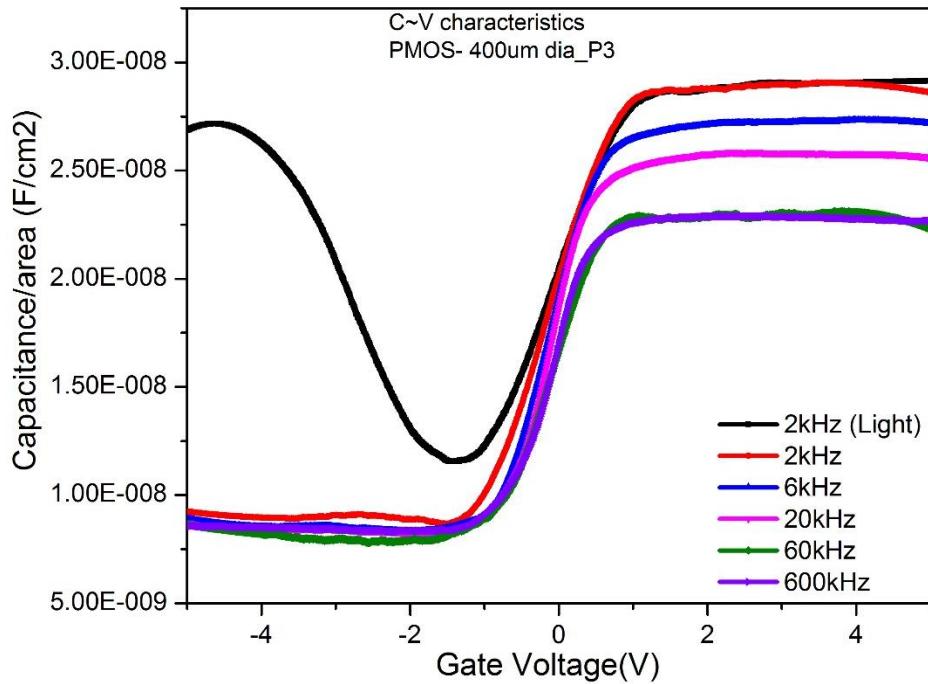

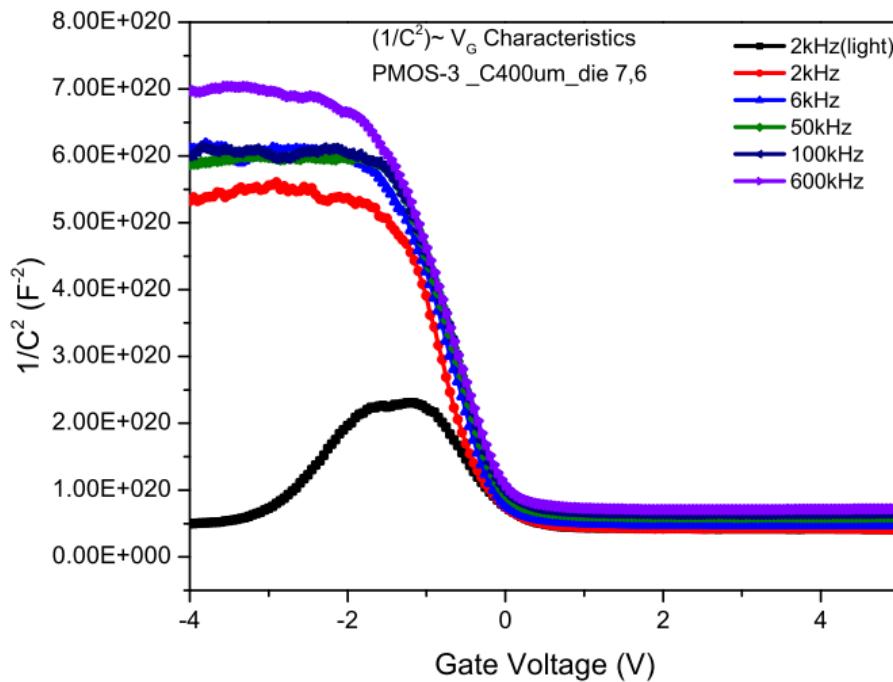

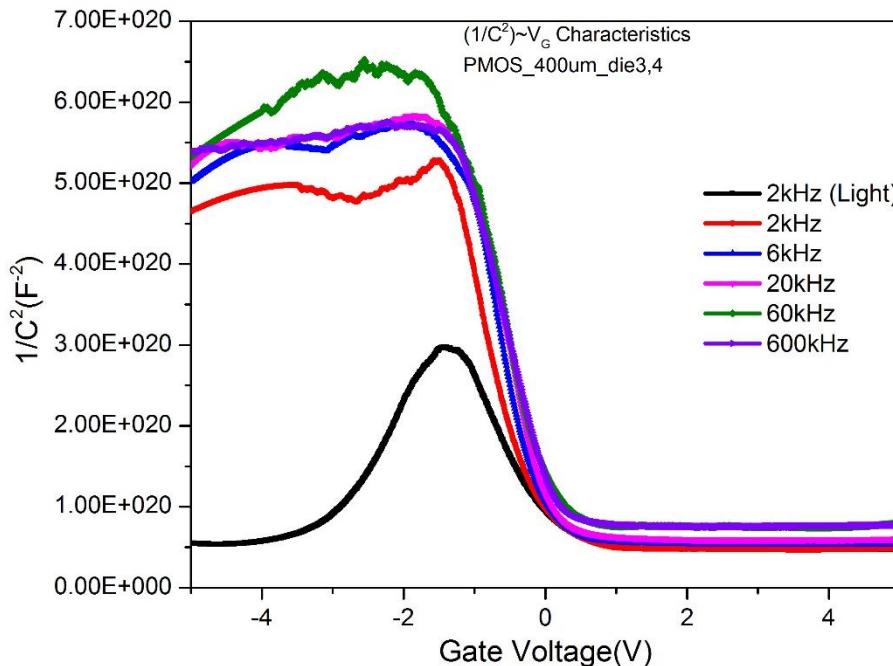

| 3.7.1 | PMOS .....                             | 127 |

| 3.7.2 | NMOS .....                             | 133 |

| 3.8   | Effect of Substrate Biasing.....       | 141 |

| 3.9   | Subthreshold Voltage Swing .....       | 145 |

| 3.10  | On State Resistance .....              | 146 |

| 3.11  | Failure Analysis.....                  | 149 |

| 4.    | Summary and Conclusions .....          | 152 |

# Table of Figures

|                                                                                                                                                                                                      |    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 1.2.1 MOSFET Cross-Section .....                                                                                                                                                              | 20 |

| Figure 1.2.2 Metal Oxide Semiconductor (MOS) Capacitor structure- Oxide layer sandwiched between metal and semiconductor layers. ....                                                                | 21 |

| Figure 1.2.3 Energy band diagrams of ideal ( $\phi_{ms} = 0$ ) p- and n-MOS structure under zero bias condition [1].....                                                                             | 22 |

| Figure 1.2.4 Band Structure of NMOS Capacitor in Accumulation condition where $V_G < 0$ [2].                                                                                                         | 23 |

| Figure 1.2.5 Band Structure of NMOS Capacitor in Depletion regime, where applied voltage $V_T > V_G > 0$ [2]. .....                                                                                  | 24 |

| Figure 1.2.6 Band Structure of NMOS Capacitor at the onset of Strong Inversion regime with applied voltage to the metal electrode $V_G = V_T$ [2]. .....                                             | 25 |

| Figure 1.2.7 Variation of surface charge density $Q_s$ as a function of surface potential $\psi_s$ for a p-type Si substrate with $N_A = 4 \times 10^{15} \text{ cm}^{-3}$ [1]. .....                | 26 |

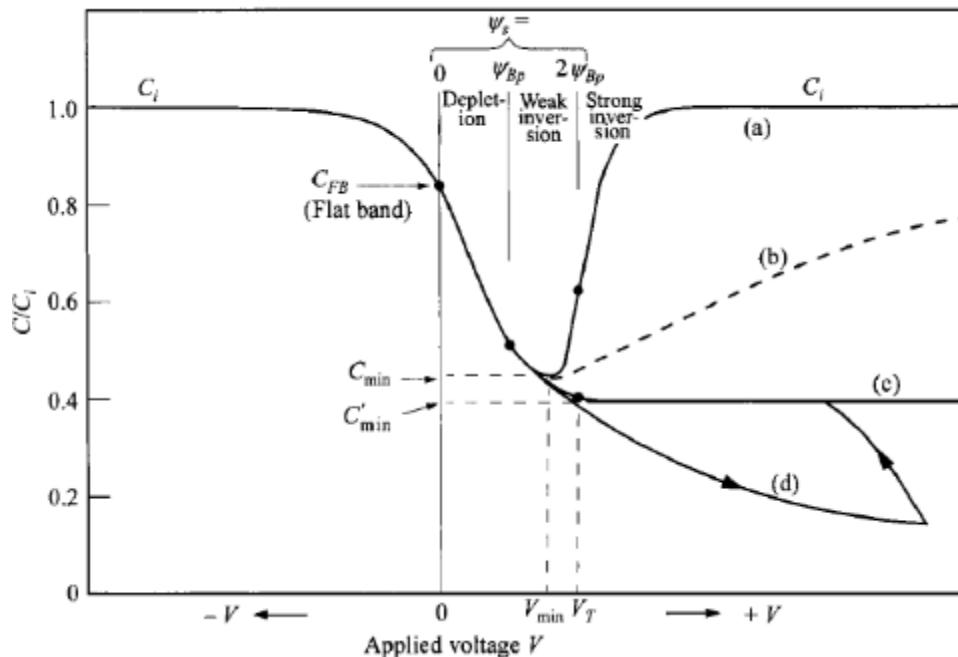

| Figure 1.2.8 Capacitance-Voltage characteristic of an NMOS with various bias regimes- accumulation, depletion, weak inversion, strong inversion and deep depletion indicated on the curve [1]. ..... | 27 |

| Figure 1.2.9. NMOSFET in various operating conditions, (a) linear regime, (b) onset of saturation and (c) Strong saturation regime [1]. .....                                                        | 30 |

| Figure 1.2.10 Ideal $I_D$ - $V_D$ characteristics of an NMOSFET with dotted lines separating the linear region, non-linear region and saturation region from each other [1]. .....                   | 31 |

| Figure 1.2.11 Simplified geometry of a short channel FET .....                                                                                                                                       | 34 |

| Figure 1.2.12 Punchthrough between source and drain. ....                                                                                                                                            | 35 |

| Figure 1.3.1 Physical structure of $\text{SiO}_2$ .....                                                                                                                                              | 38 |

|                                                                                                                                                                                                                           |    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 1.3.2 Final Si surface after oxidation.....                                                                                                                                                                        | 39 |

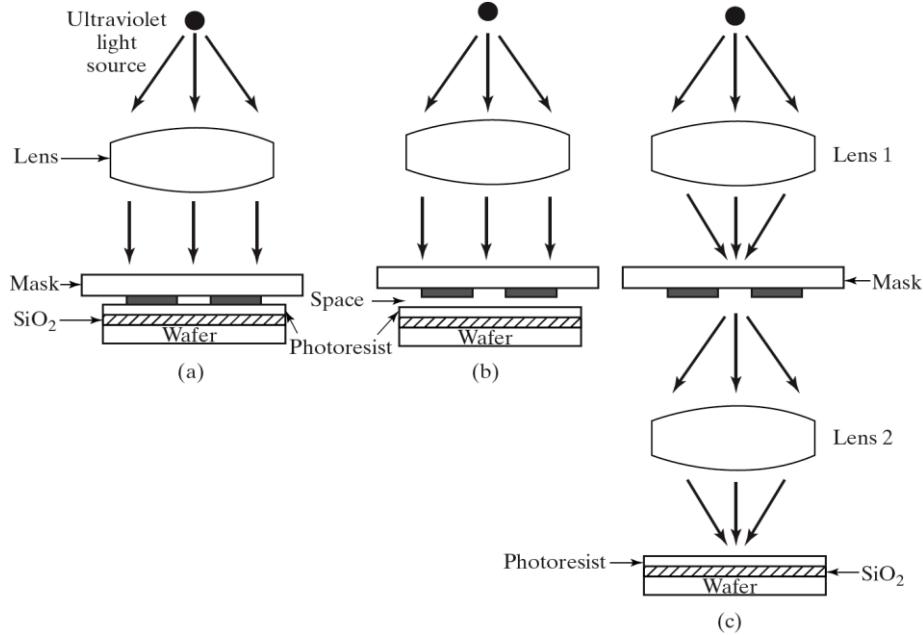

| Figure 1.3.3 Three basic methods of exposure .....                                                                                                                                                                        | 42 |

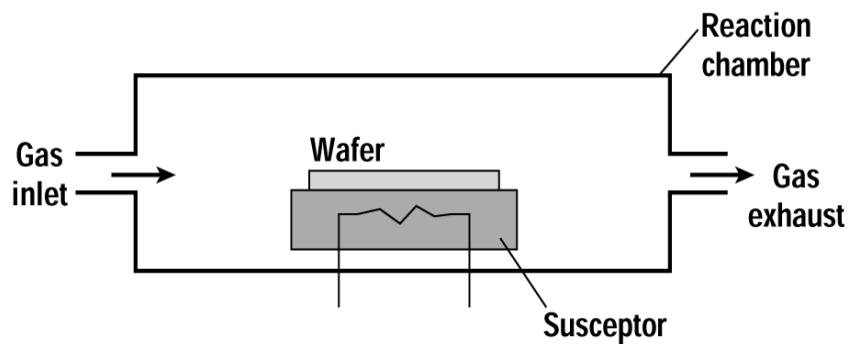

| Figure 1.3.4 Simple CVD system .....                                                                                                                                                                                      | 43 |

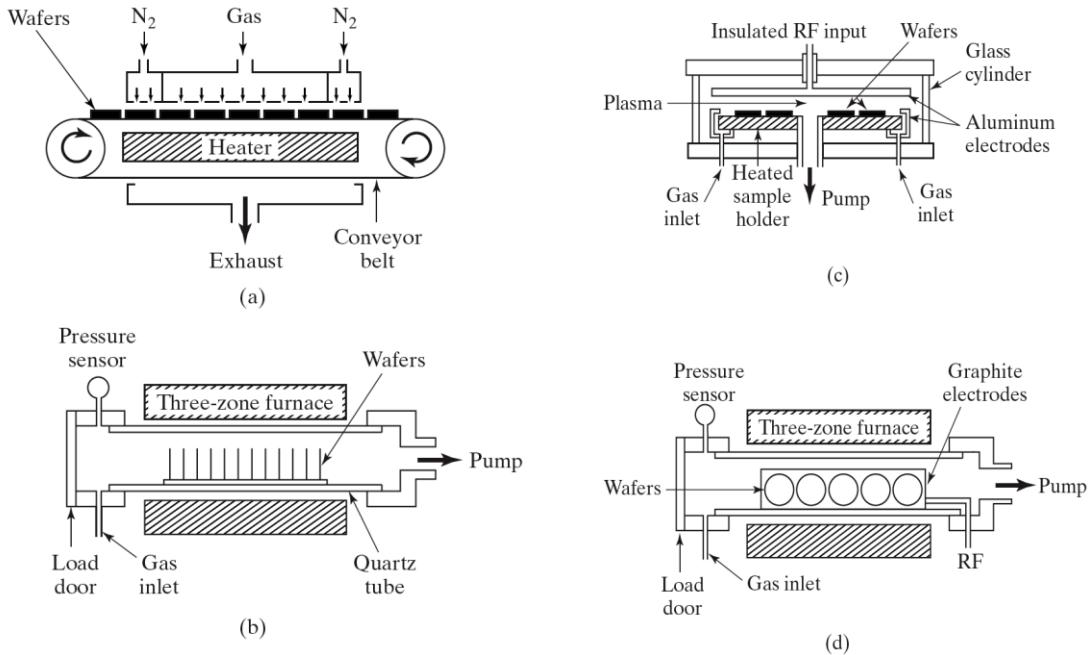

| Figure 1.3.5 (a) APCVD (b) LPCVD (c) parallel-plate (d) PECVD systems .....                                                                                                                                               | 44 |

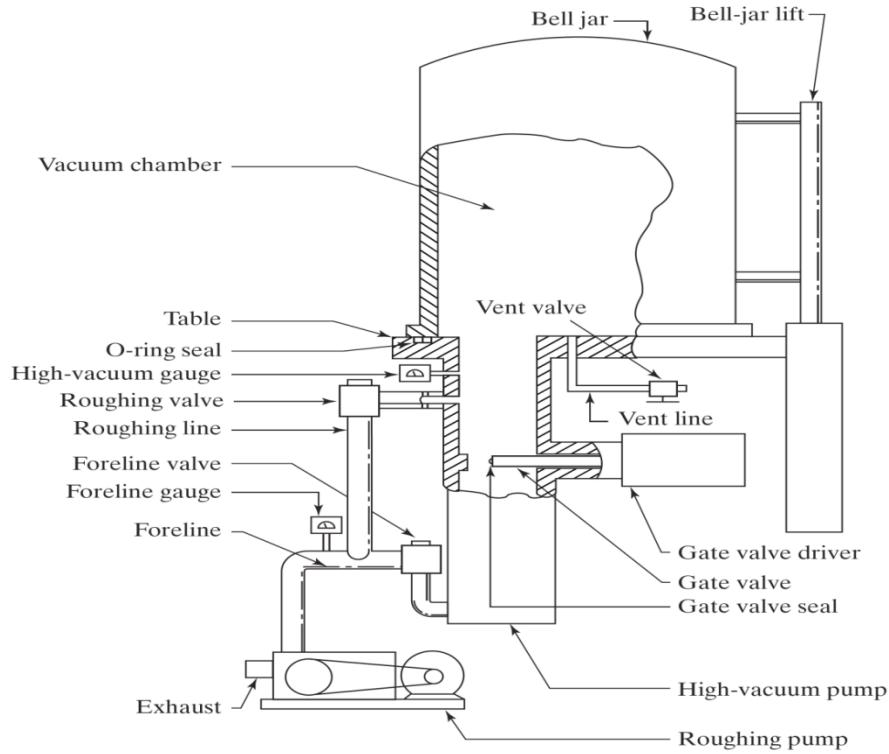

| Figure 1.3.6 Typical evaporation vacuum .....                                                                                                                                                                             | 45 |

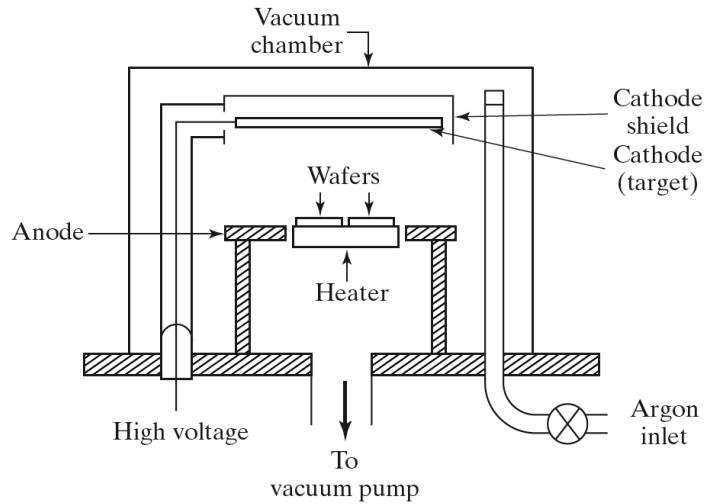

| Figure 1.3.7 Sputtering chamber.....                                                                                                                                                                                      | 46 |

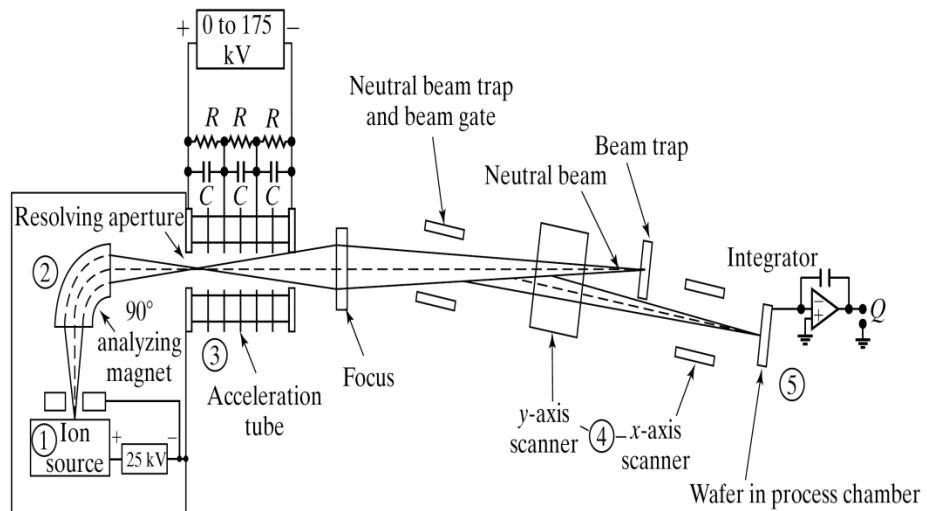

| Figure 1.3.8 Ion implantation system .....                                                                                                                                                                                | 48 |

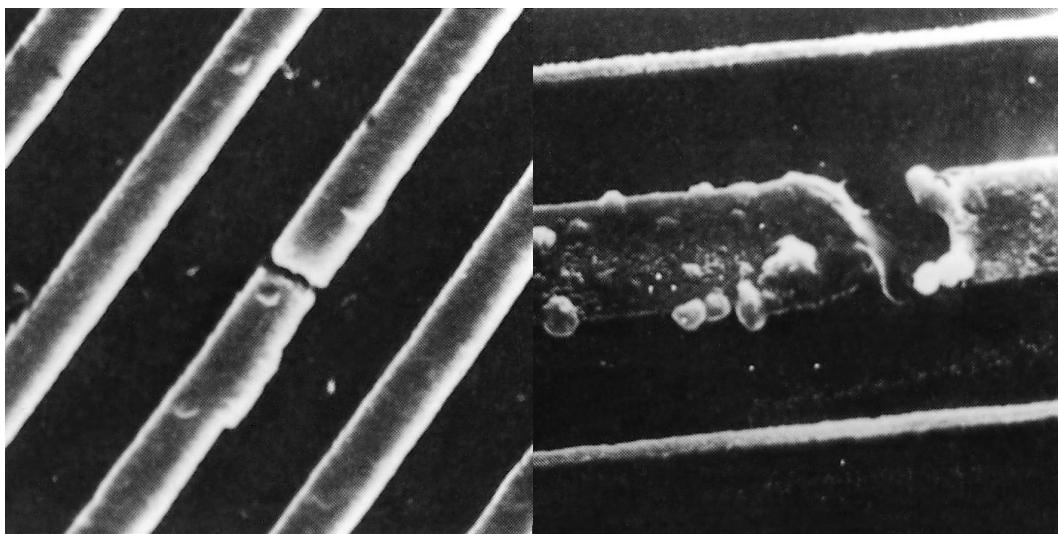

| Figure 1.3.9 SEM images of failure due to interconnections .....                                                                                                                                                          | 50 |

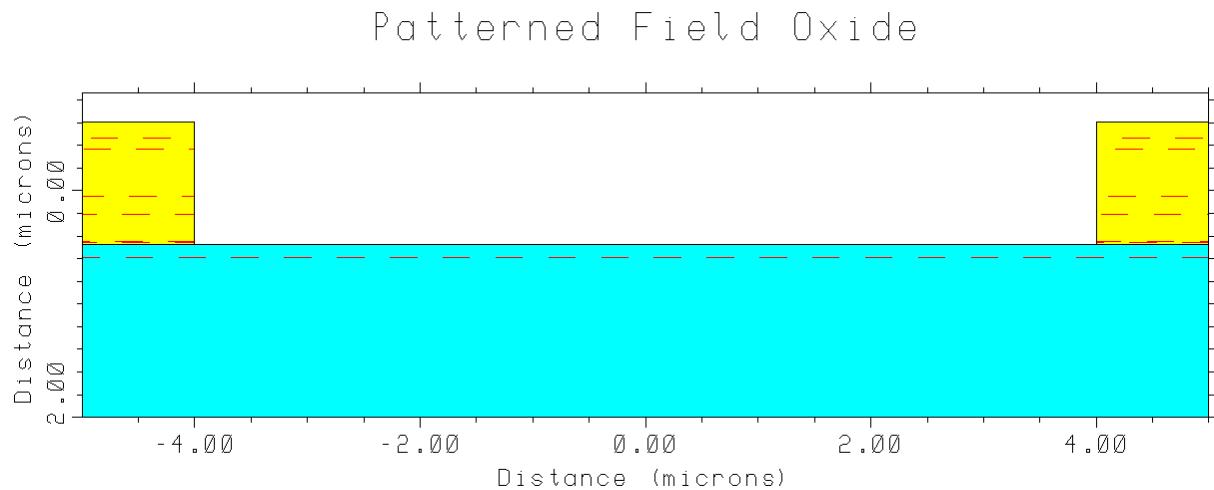

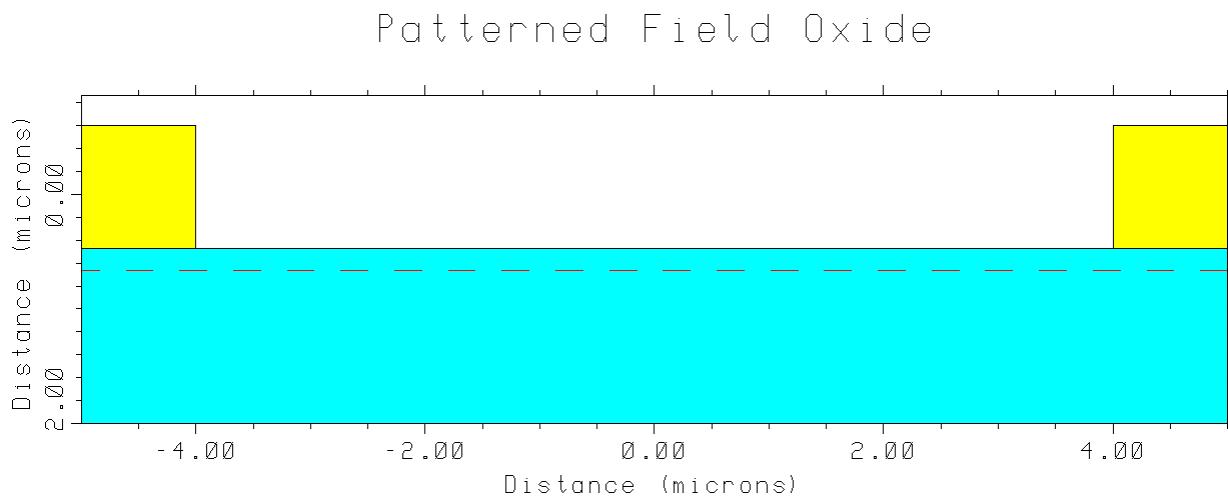

| Figure 1.4.1 Cross-section of patterned field oxide from TSUPREM simulations. ....                                                                                                                                        | 54 |

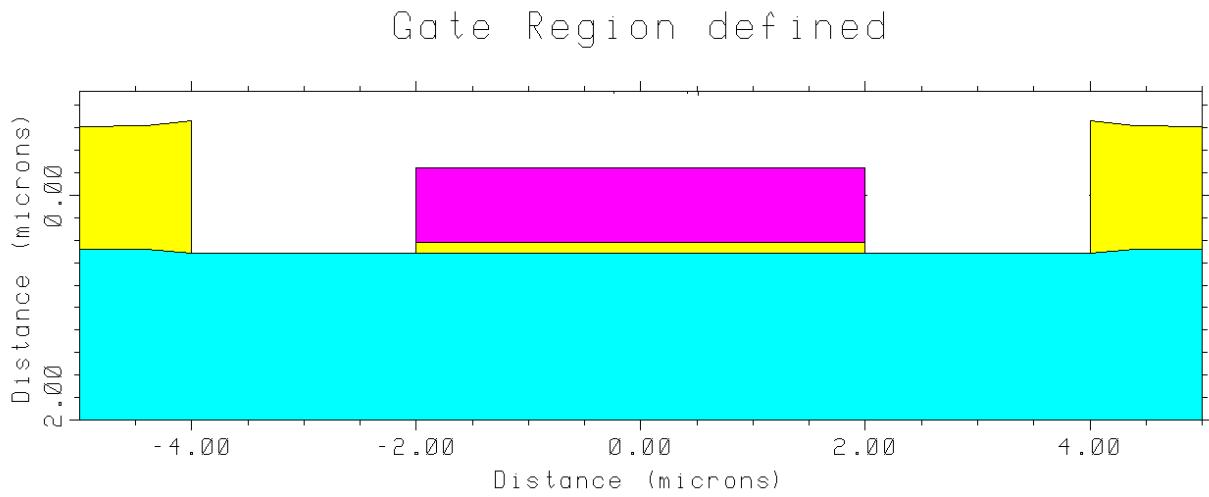

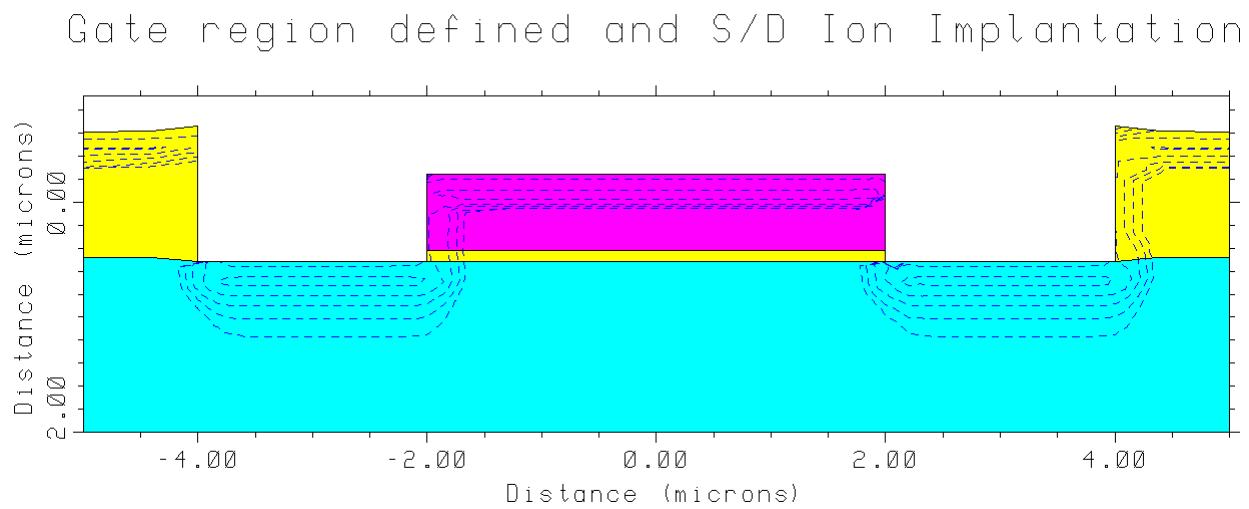

| Figure 1.4.2 Cross-section of patterned gate oxide and polysilicon defining source and drain region from TSUPREM simulations.....                                                                                         | 57 |

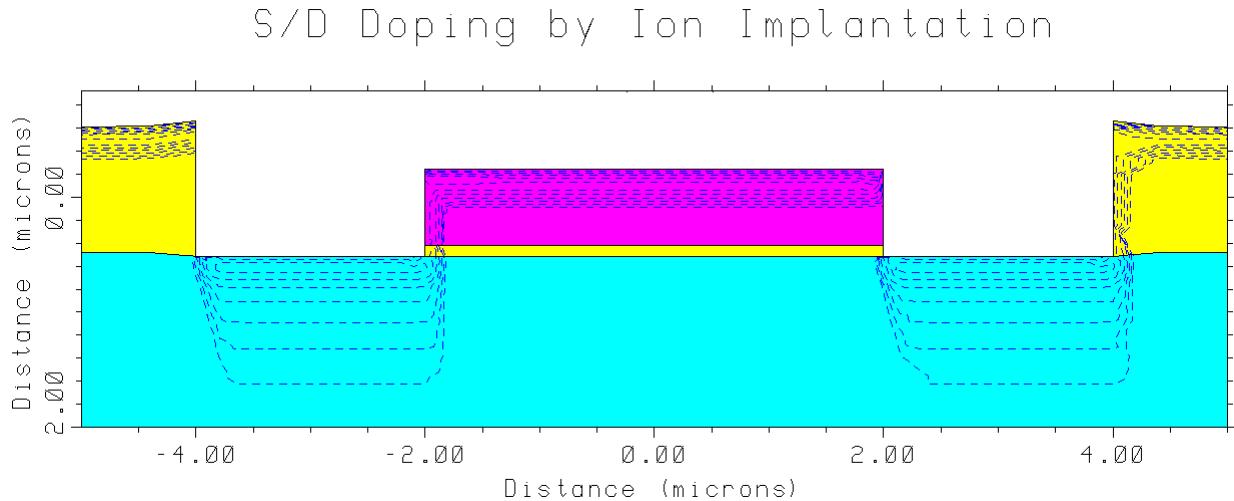

| Figure 1.4.3 Cross-section of patterned gate oxide and polysilicon with doped source and drain region from TSUPREM simulations.....                                                                                       | 57 |

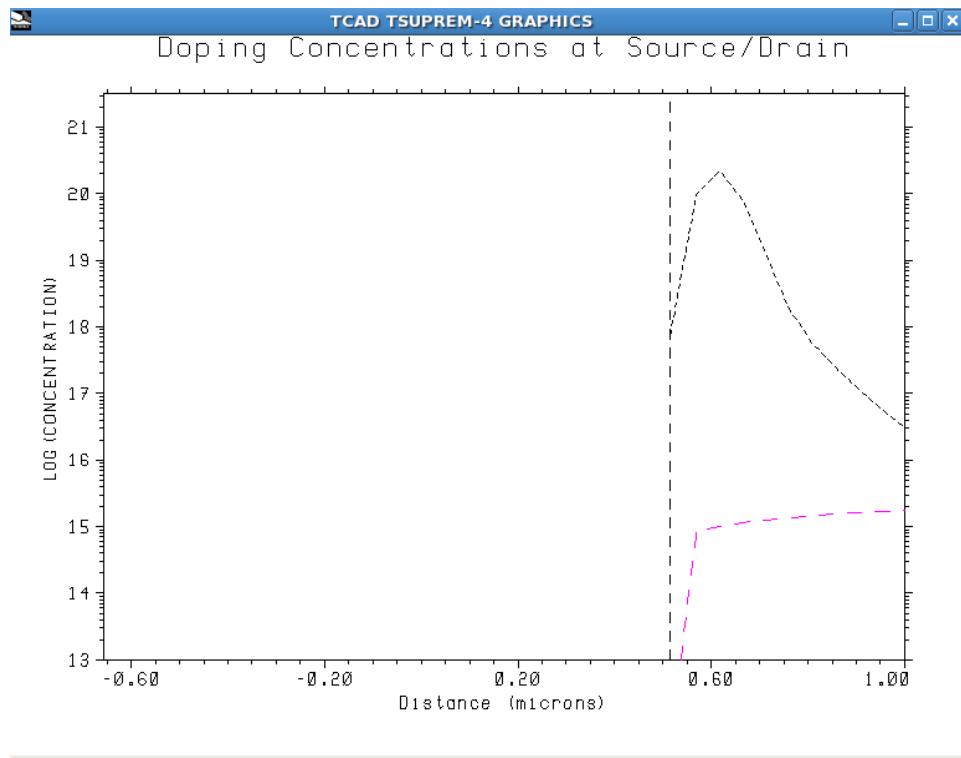

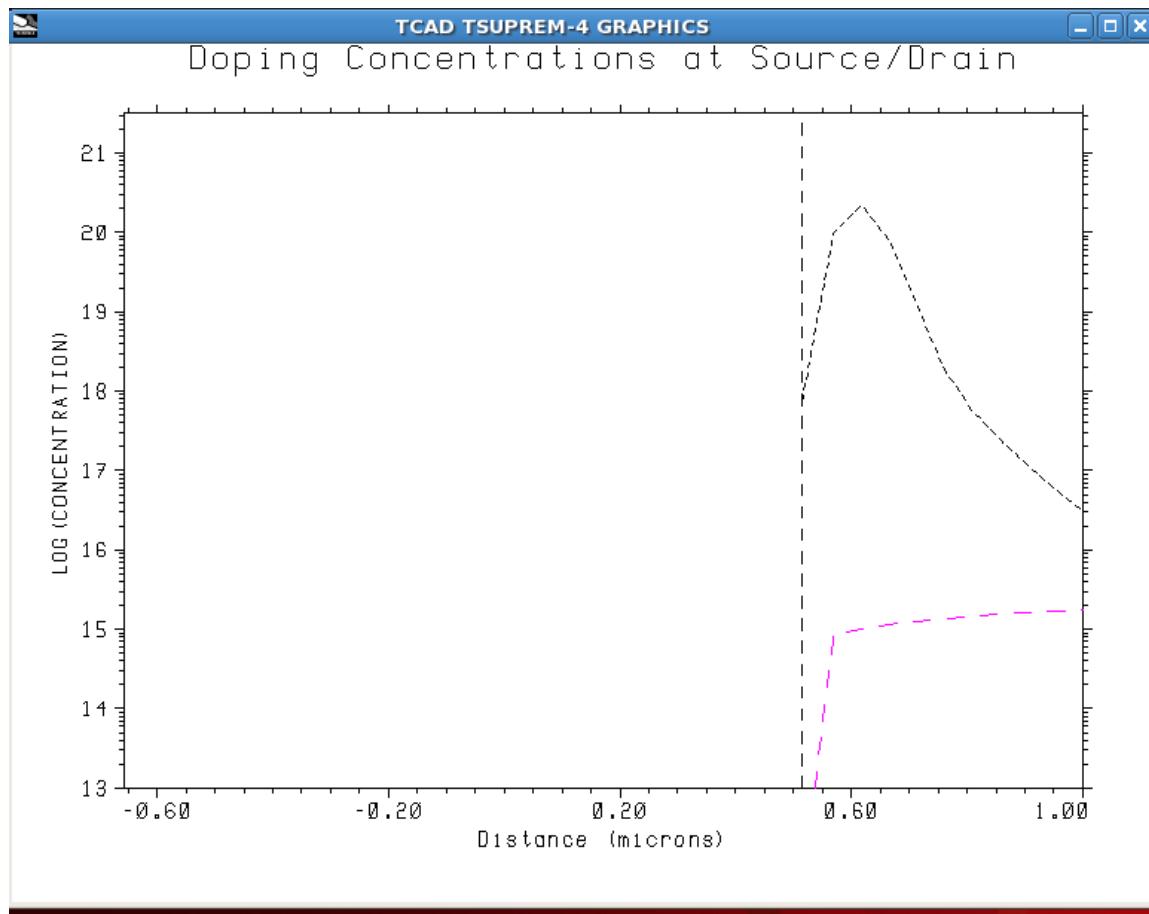

| Figure 1.4.4 Doping concentration in source and drain with black dotted line showing $\log_{10}$ (As concentration) and red dotted line showing $\log_{10}$ (B concentration). ....                                       | 58 |

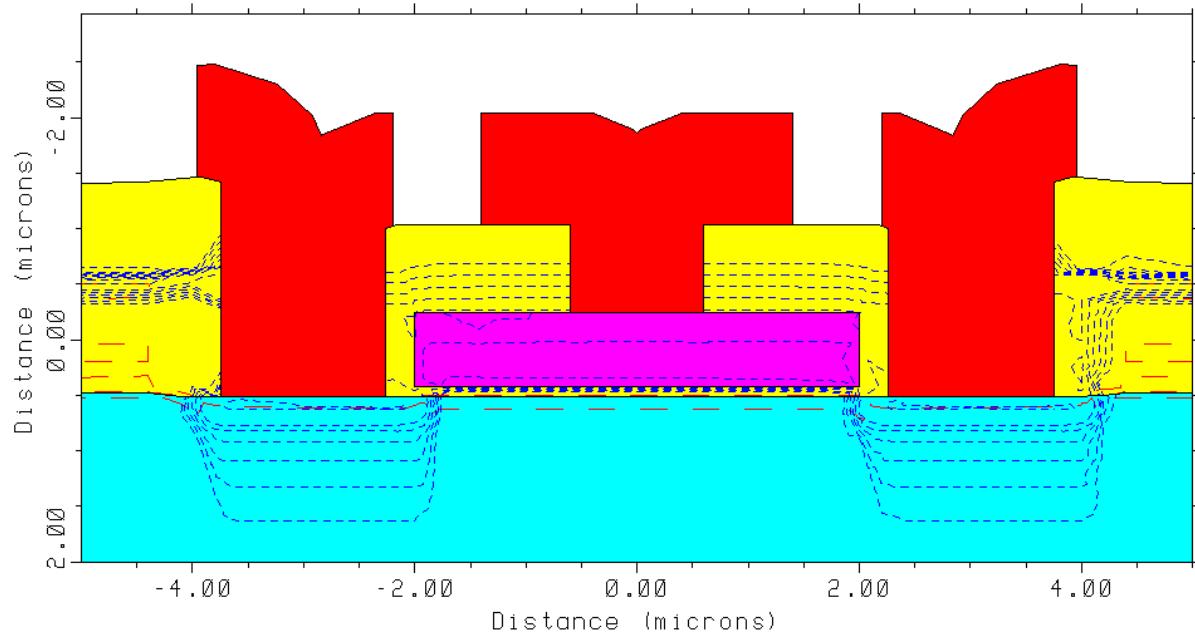

| Figure 1.4.5 NMOS final device structure after ILD and metal deposition and patterning with arsenic and boron concentrations with red showing aluminum, yellow showing oxide, pink showing poly and blue showing Si. .... | 61 |

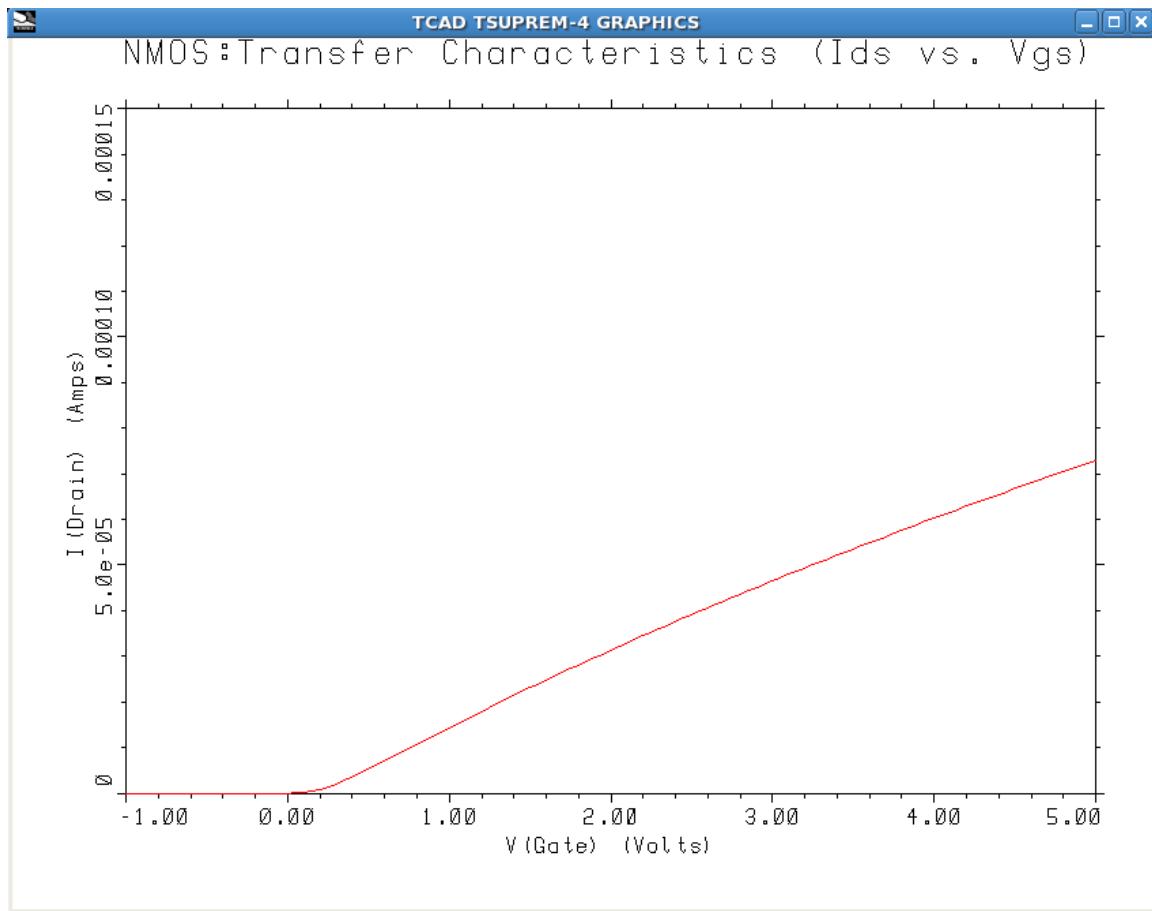

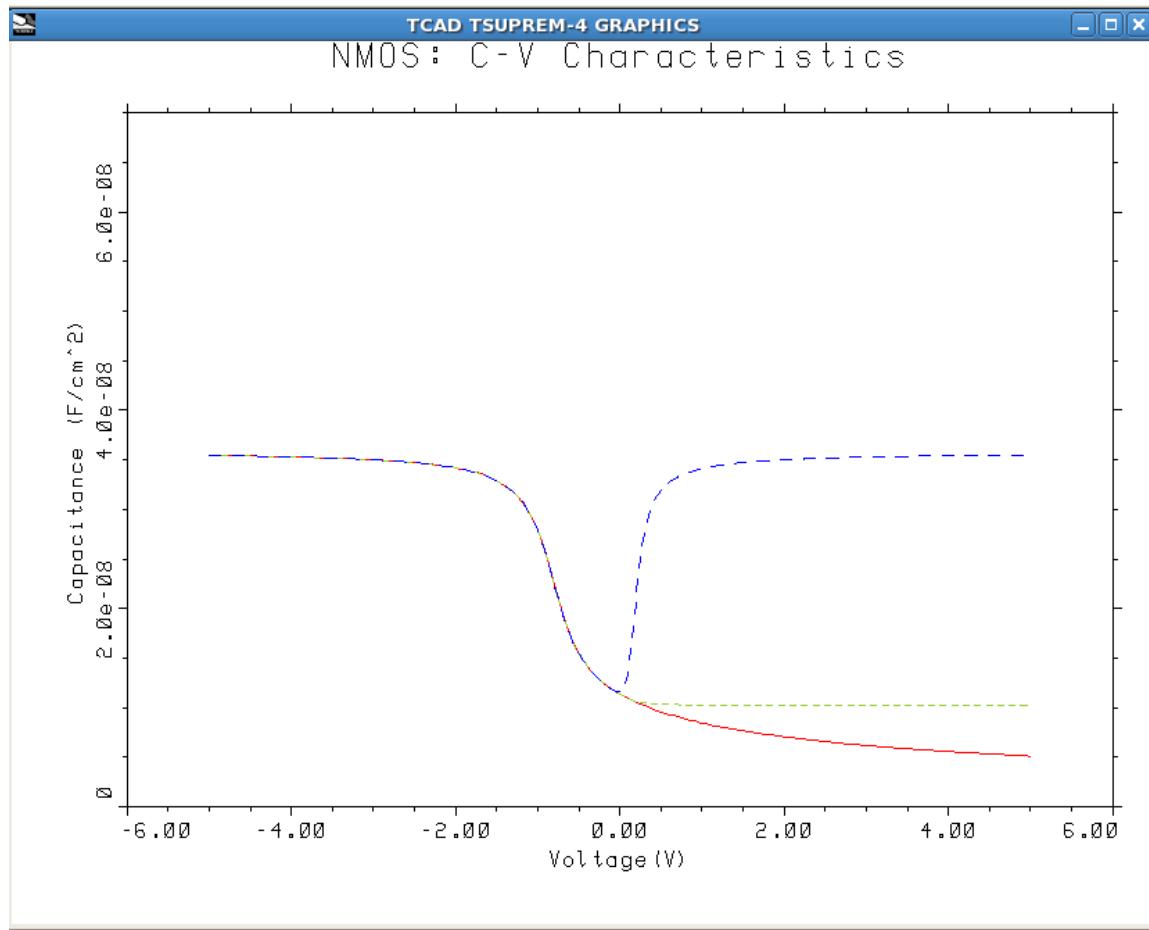

| Figure 1.4.6 NMOSFET with $L=4\mu m$ simulated transfer characteristics with $V_{th} = \sim 0.1V$ .....                                                                                                                   | 63 |

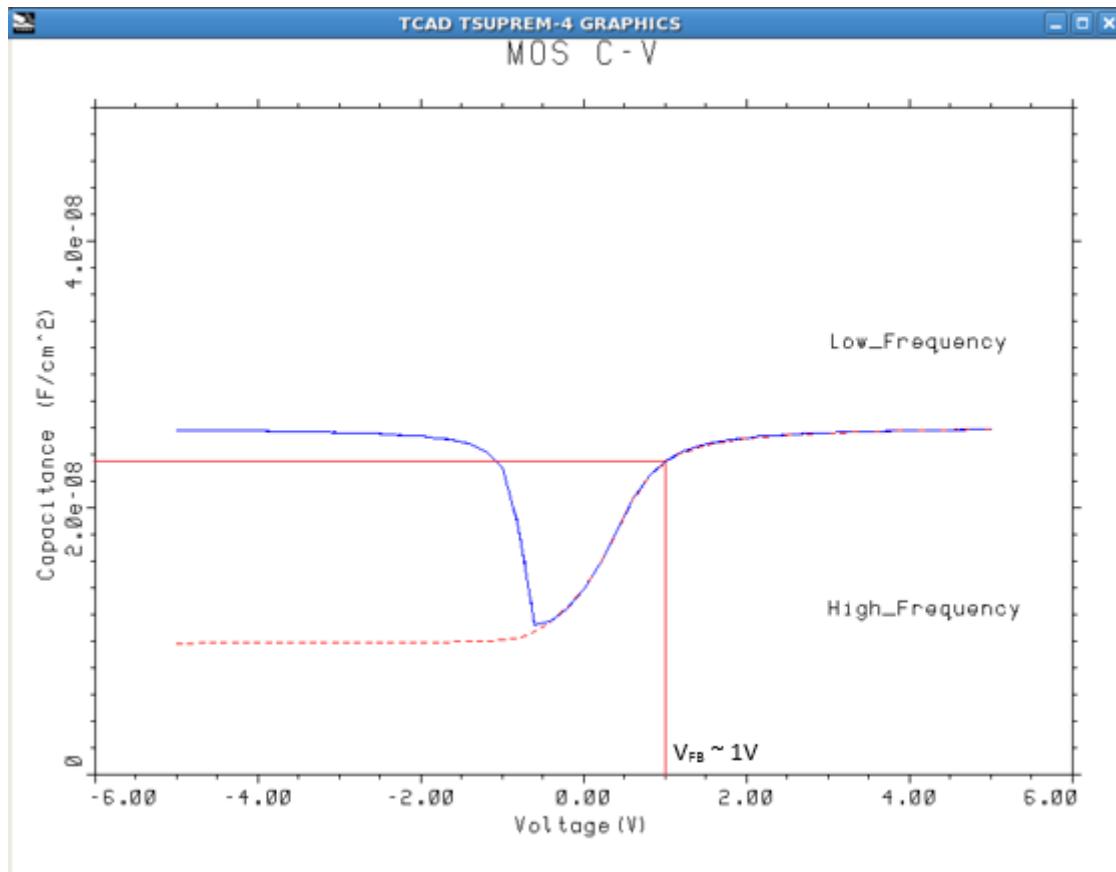

| Figure 1.4.7 NMOSFET with $L=4\mu m$ simulated C~V characteristics in low, high frequencies as well as deep depletion.....                                                                                                | 64 |

| Figure 1.4.8 Cross-section of patterned gate oxide and polysilicon defining source and drain region from TSUPREM simulations.....                                                                                         | 68 |

|                                                                                                                                                                                                                                                     |    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 1.4.9 Cross-section of patterned gate oxide and polysilicon with boron doped source and drain region from TSUPREM simulations. ....                                                                                                          | 71 |

| Figure 1.4.10 Doping concentration in source and drain with black dotted line showing $\log_{10}$ (B concentration) and red dotted line showing $\log_{10}$ (Phosphorous concentration). ....                                                       | 72 |

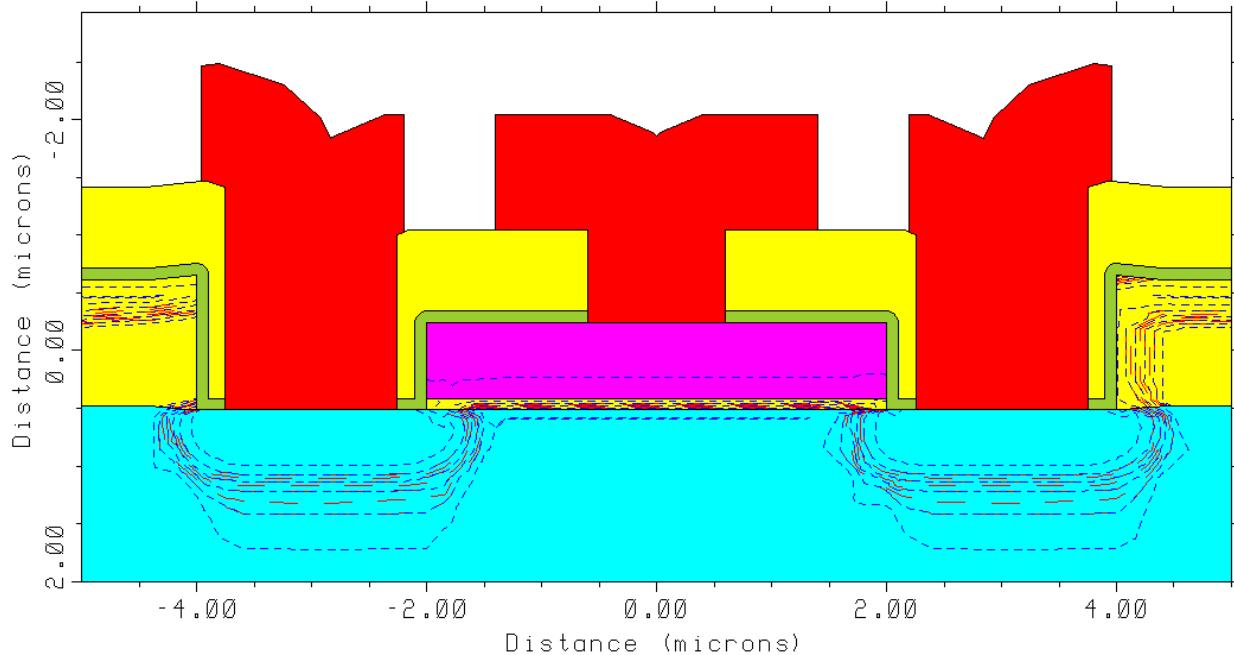

| Figure 1.4.11 PMOS final device structure after ILD and metal deposition and patterning with boron and phosphor concentrations, green layer showing nitride, red showing aluminum, yellow showing oxide, pink showing poly and blue showing Si..... | 75 |

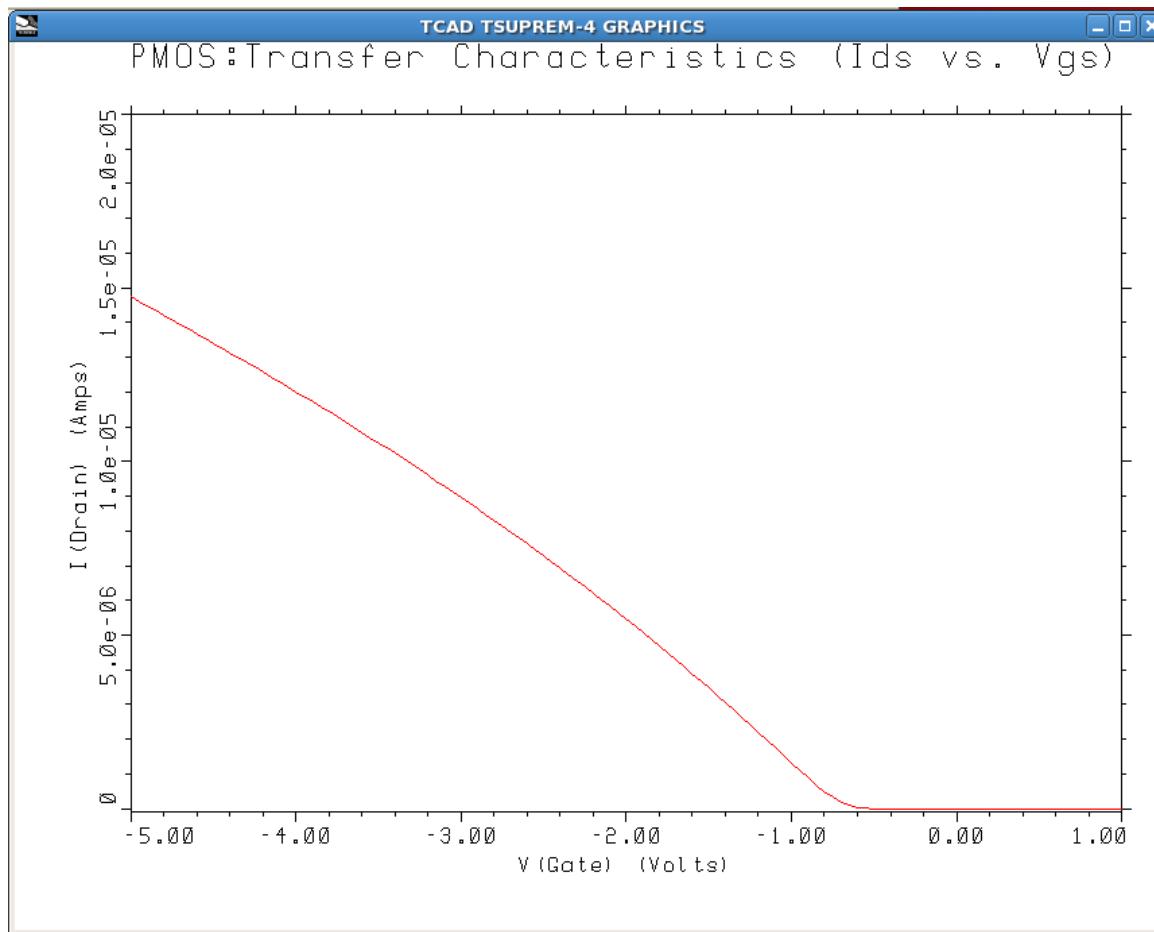

| Figure 1.4.12 PMOSFET with $L=4\mu\text{m}$ simulated transfer characteristics with $V_{\text{th}} = \sim -0.5\text{V}$ . ...                                                                                                                       | 77 |

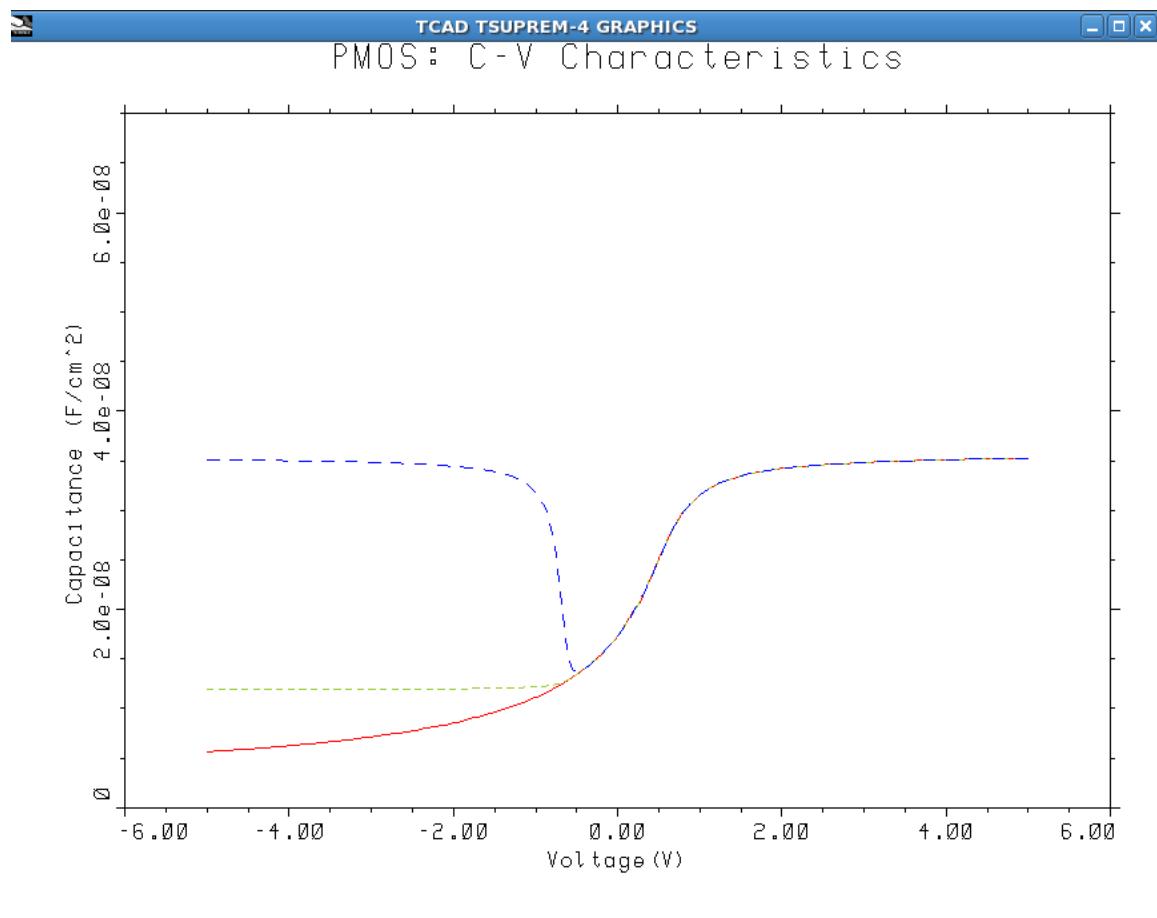

| Figure 1.4.13 PMOSFET with $L=4\mu\text{m}$ simulated C~V characteristics in low, high frequencies as well as deep depletion.....                                                                                                                   | 78 |

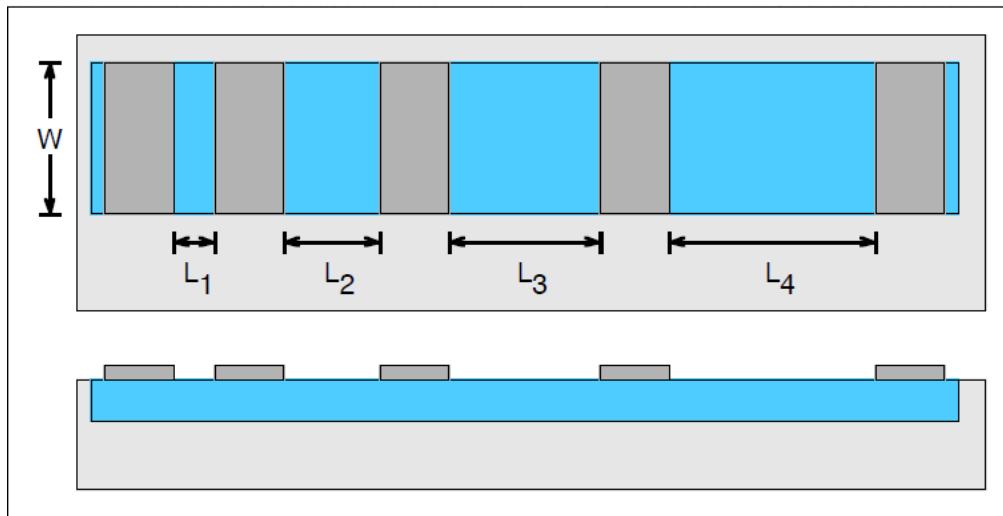

| Figure 1.5.1 TLM set-up for determining contact and sheet resistance.....                                                                                                                                                                           | 79 |

| Figure 1.5.2 TLM for estimating $R_c$ and $R_s$ .....                                                                                                                                                                                               | 80 |

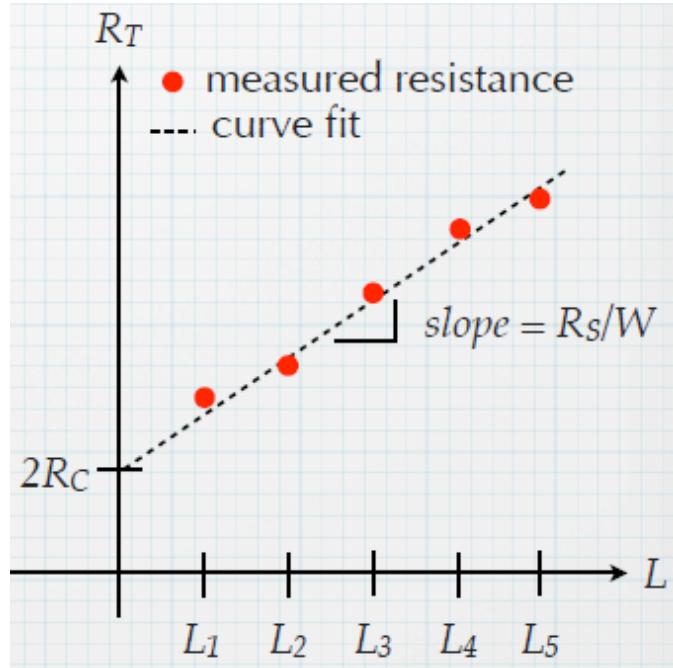

| Figure 1.5.3 Kelvin structure for measuring contact resistivity.....                                                                                                                                                                                | 81 |

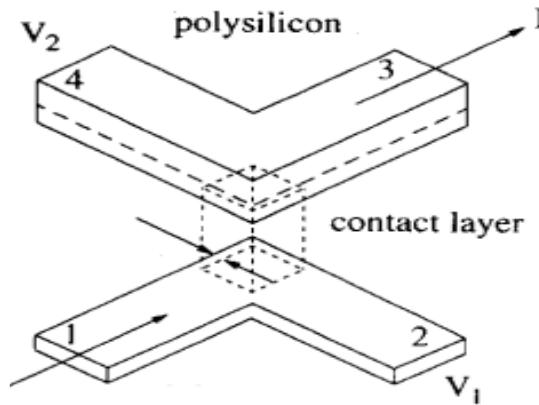

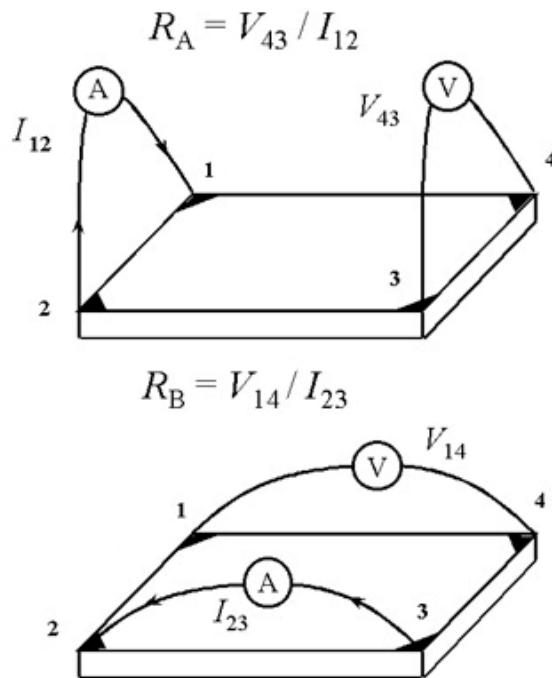

| Figure 1.5.4 Probe arrangement for VdP measurements .....                                                                                                                                                                                           | 82 |

| Figure 1.5.5 Voltmeter and Ammeter placement.....                                                                                                                                                                                                   | 82 |

| Figure 1.5.6 $I_{\text{DS}}-V_{\text{DS}}$ output characteristics of a MOSFET .....                                                                                                                                                                 | 85 |

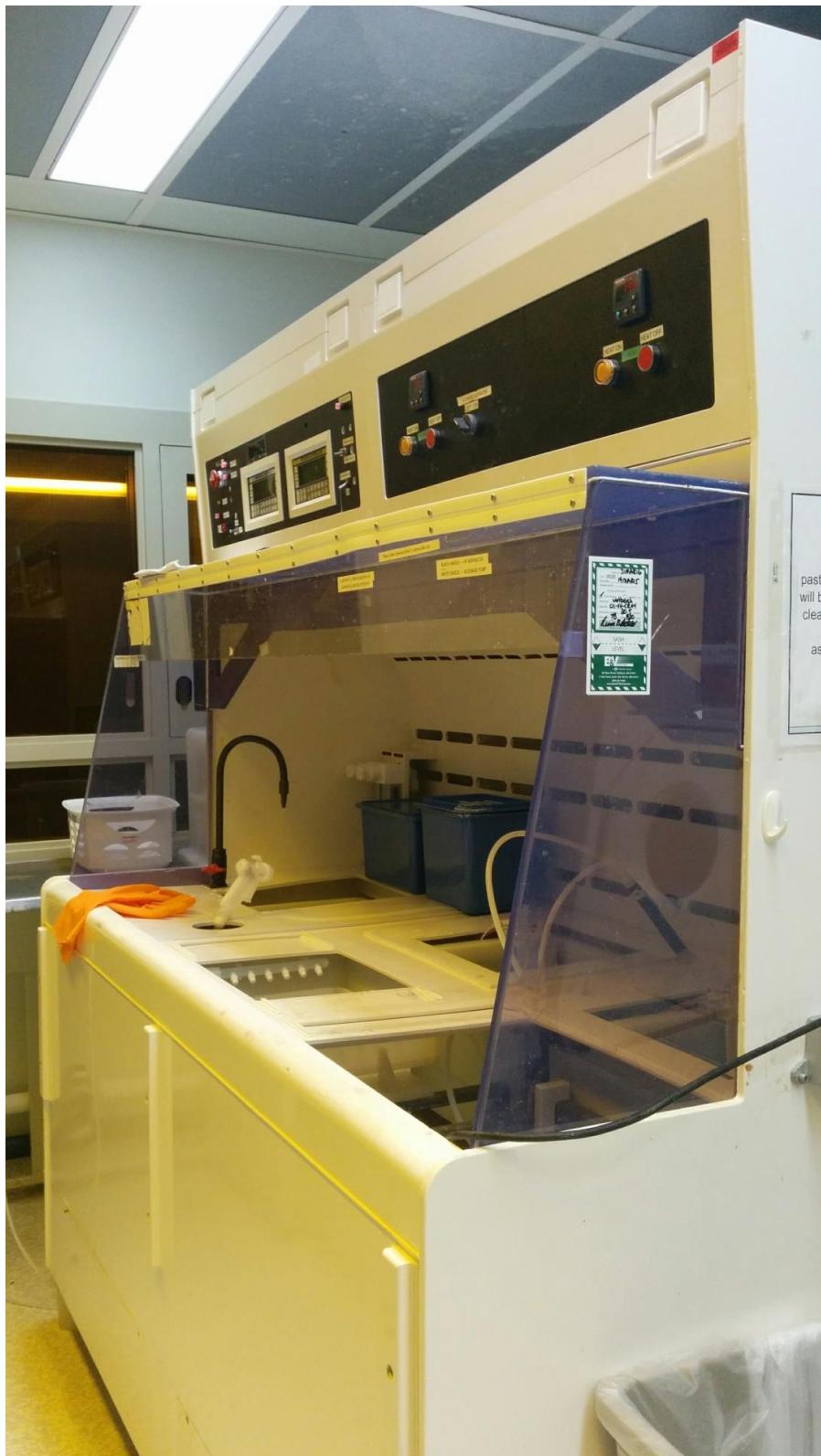

| Figure 2.1.1 Wet bench for RCA clean.....                                                                                                                                                                                                           | 89 |

| Figure 2.1.2 Bruce furnace for oxide growth.....                                                                                                                                                                                                    | 90 |

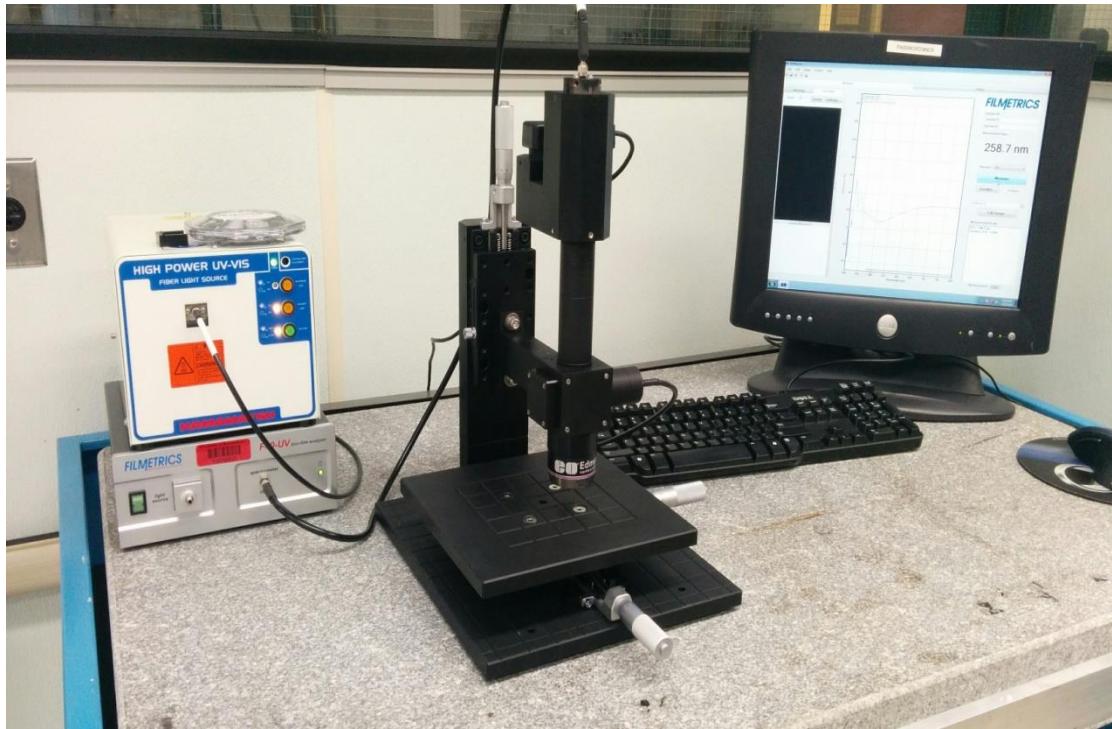

| Figure 2.2.1 Filmetrics F40-UV Interferometer .....                                                                                                                                                                                                 | 92 |

| Figure 2.2.2 Headway spinner .....                                                                                                                                                                                                                  | 93 |

| Figure 2.2.3 OAI aligner.....                                                                                                                                                                                                                       | 94 |

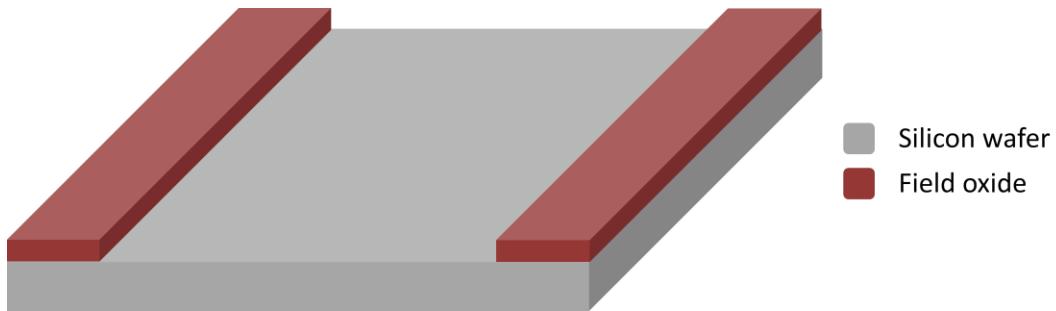

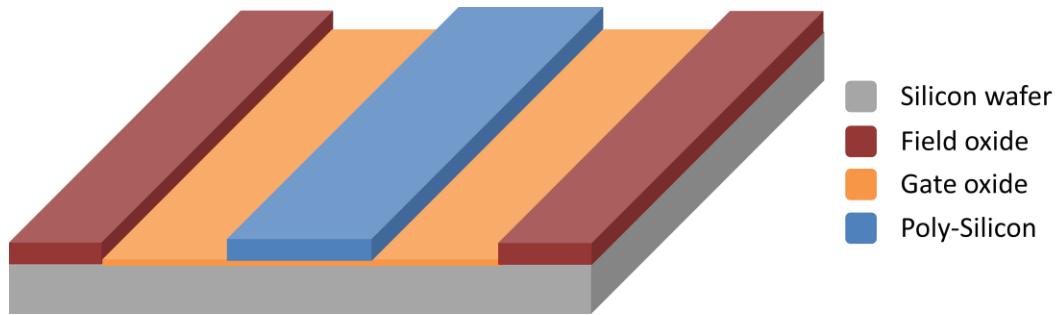

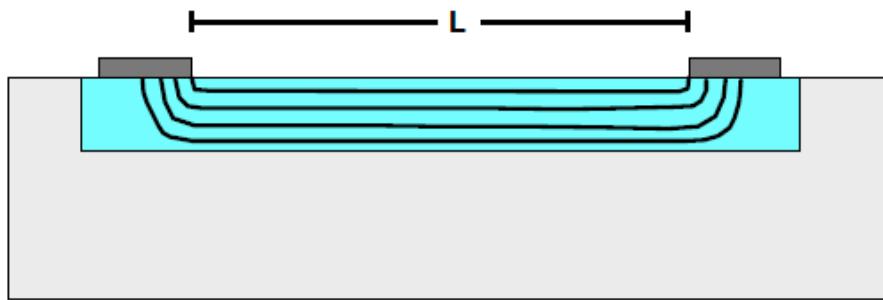

| Figure 2.2.4 Schematic of a MOSFET after active area definition. ....                                                                                                                                                                               | 96 |

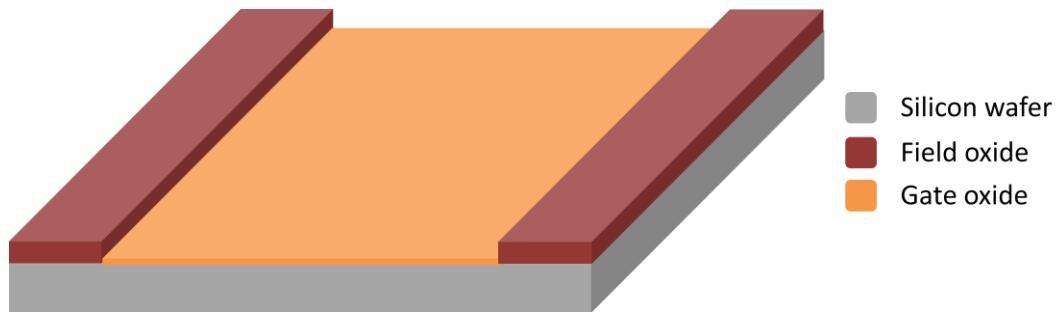

| Figure 2.3.1 Schematic of a MOSFET after gate oxidation. ....                                                                                                                                                                                       | 97 |

|                                                                                               |     |

|-----------------------------------------------------------------------------------------------|-----|

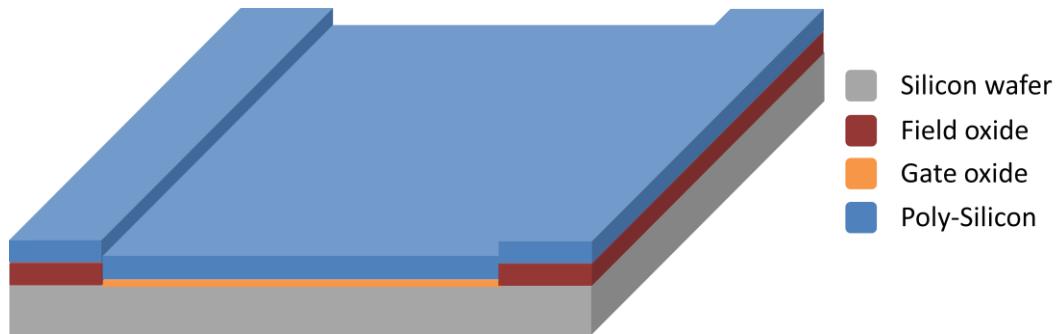

| Figure 2.3.2 Schematic of a MOSFET after poly-Si deposition.....                              | 98  |

| Figure 2.4.1 Adixen AMS 100 reactive ion etcher. ....                                         | 99  |

| Figure 2.4.2 Schematic of a MOSFET after poly-Si etch.....                                    | 100 |

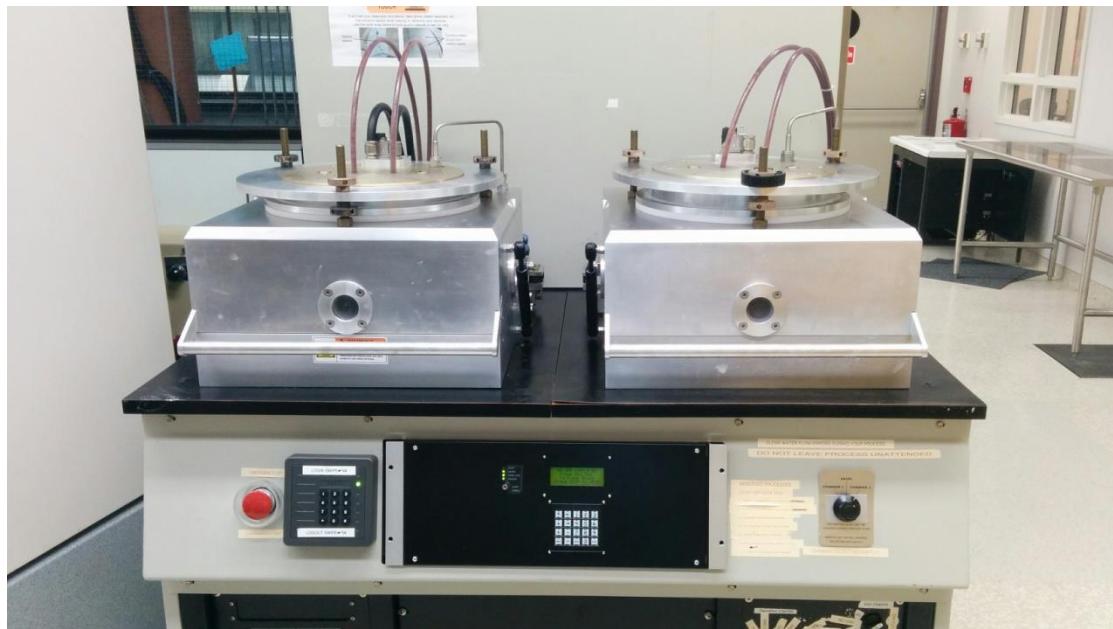

| Figure 2.6.1 Plasmatherm system (including PECVD and RIE etcher) .....                        | 104 |

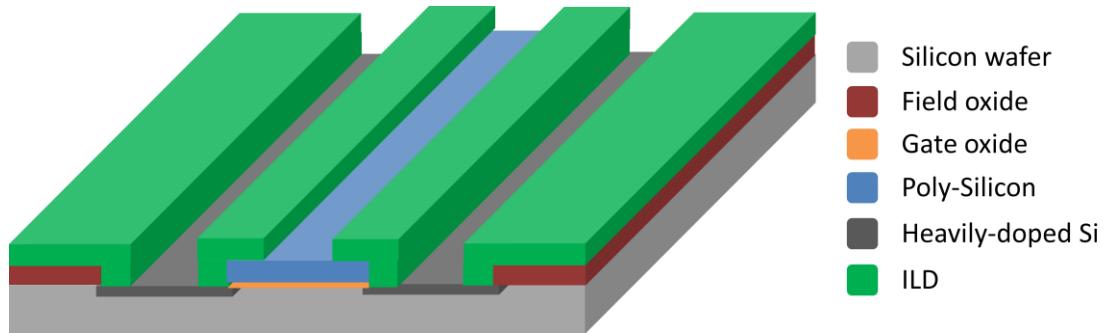

| Figure 2.6.2 Schematic of a MOSFET after ILD patterning. ....                                 | 105 |

| Figure 2.7.1 Top: Overview of the sputter tool. Bottom: Inside view of the sputter tool. .... | 106 |

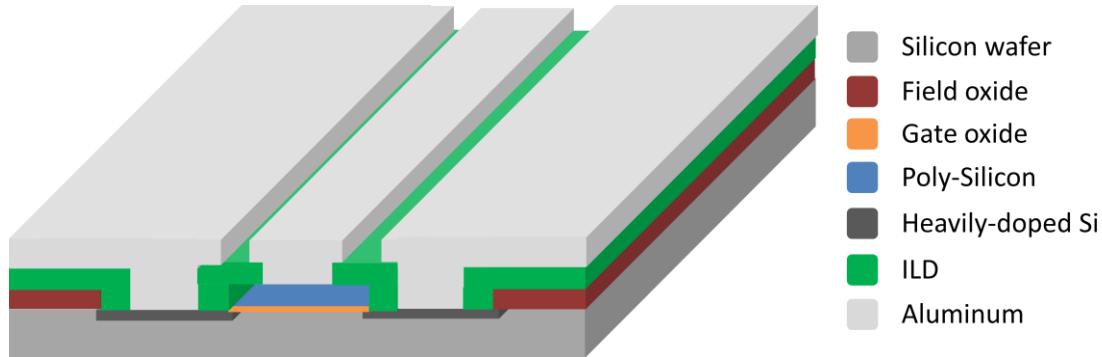

| Figure 2.7.2 Schematic of a MOSFET after metallization and etch.....                          | 107 |

| Figure 2.8.1 Schematic of a MOSFET after backside metal contact.....                          | 108 |

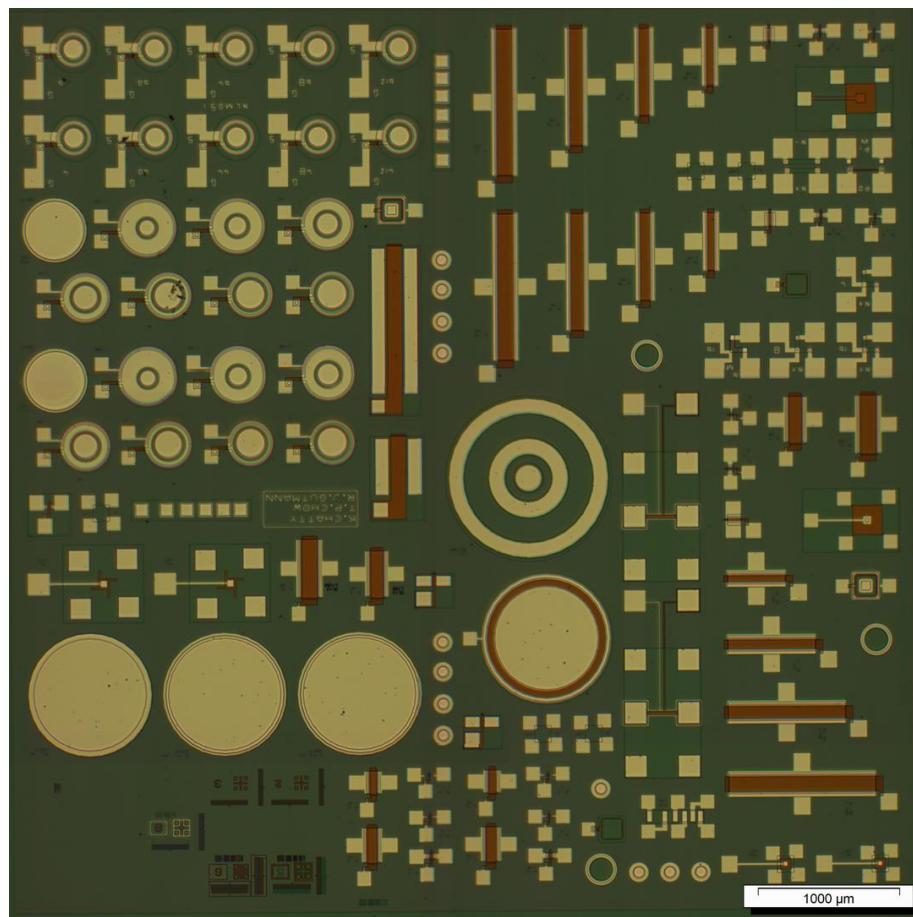

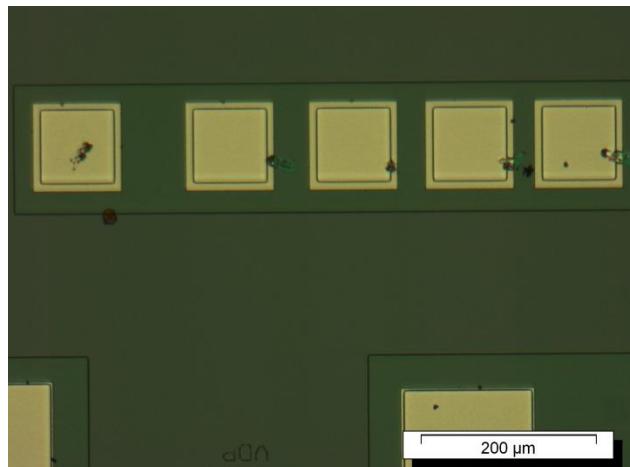

| Figure 2.8.2 Optical image of complete die after fabrication. ....                            | 109 |

| Figure 3.1.1 TLM plot for nMOS .....                                                          | 110 |

| Figure 3.1.2 TLM plots for pMOS.....                                                          | 111 |

| Figure 3.1.3 Transmission line structure used for testing.....                                | 111 |

| Figure 3.1.4 Example of resistance plot.....                                                  | 112 |

| Figure 3.1.5 Structure used for testing.....                                                  | 112 |

| Figure 3.1.6 current crowding phenomenon .....                                                | 113 |

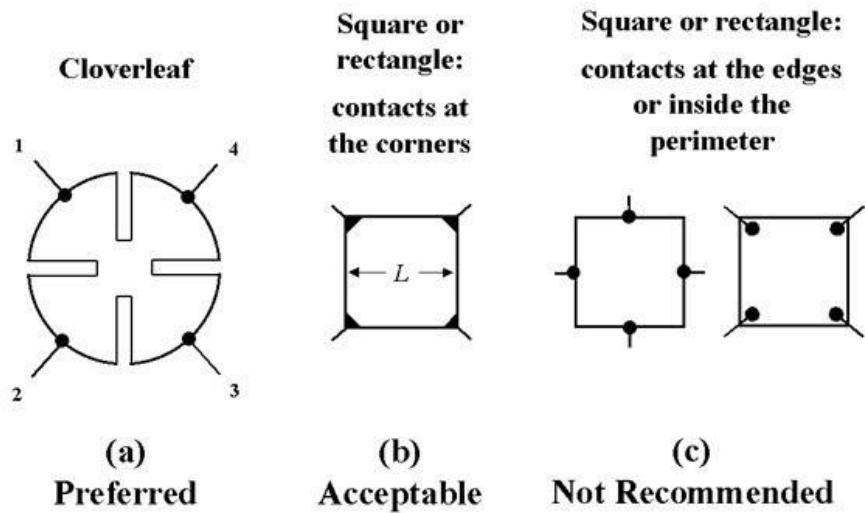

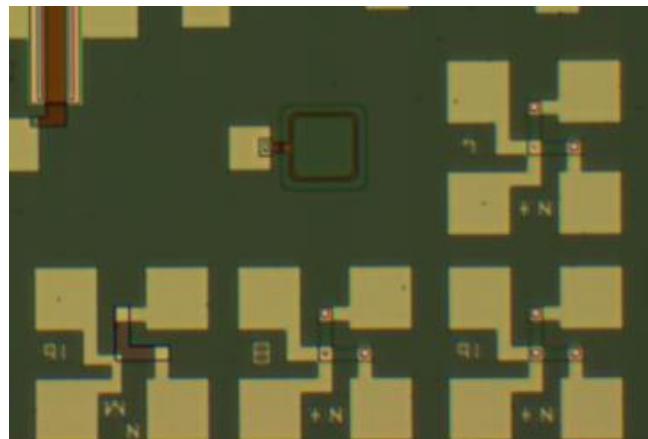

| Figure 3.2.1 Van der Pauw structure used for testing.....                                     | 113 |

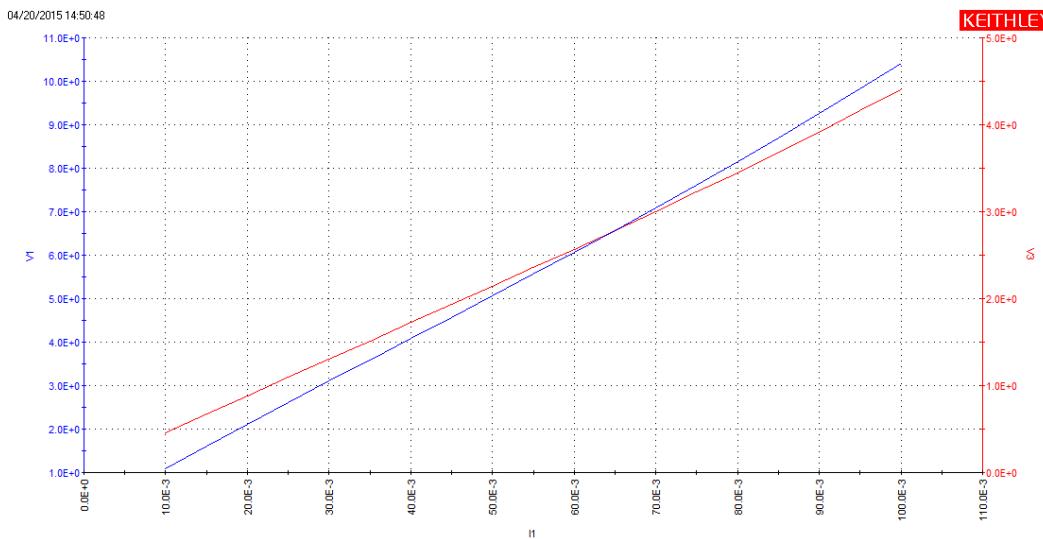

| Figure 3.2.2 characteristic plot of a VdP measurement.....                                    | 114 |

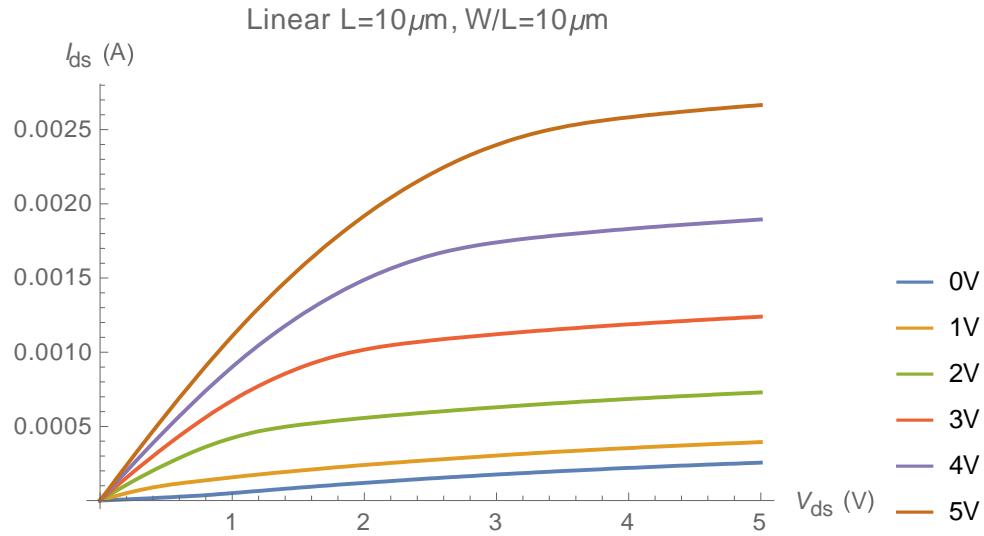

| Figure 3.3.1:Vds-Ids curves of L10, WL10 linear.....                                          | 115 |

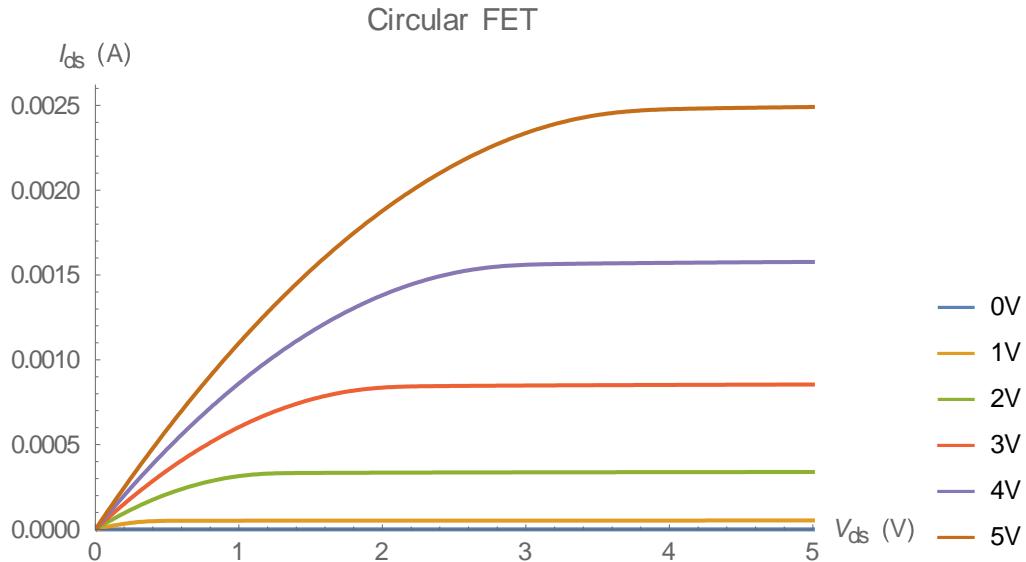

| Figure 3.3.2: Vds-Ids Curves of CFET L10 .....                                                | 115 |

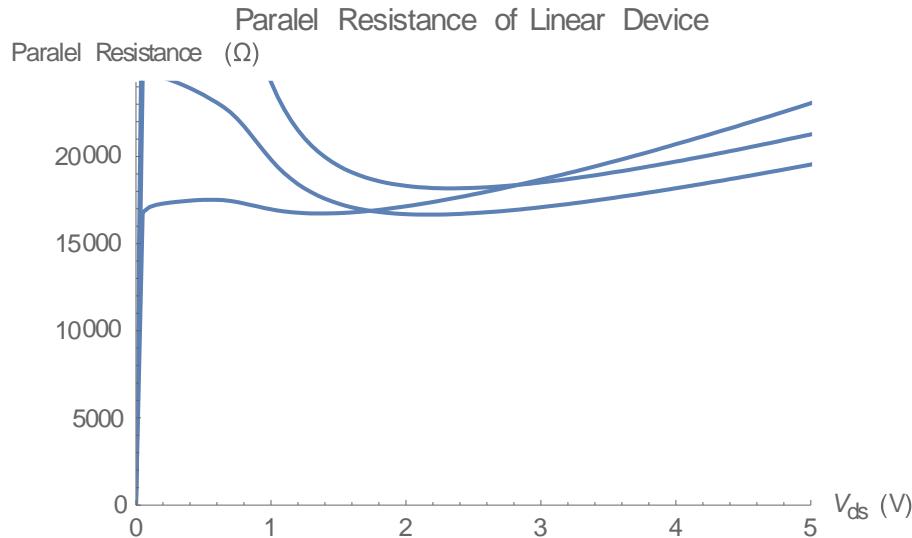

| Figure 3.3.3: Parallel Resistance of Linear Device.....                                       | 116 |

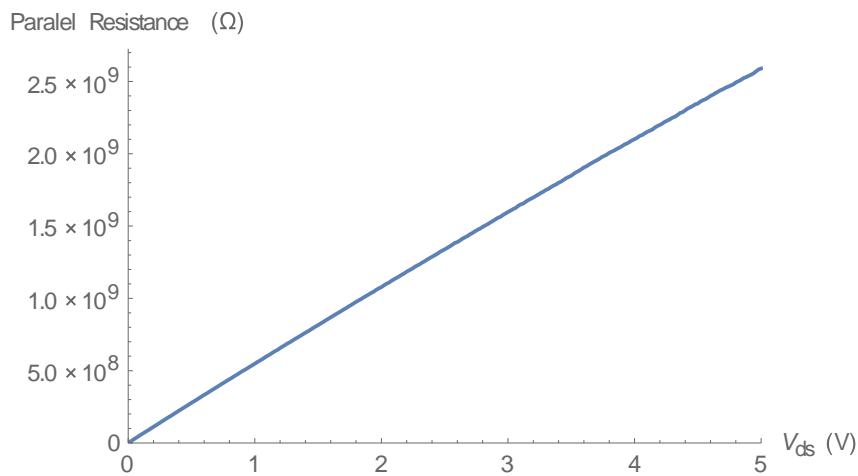

| Figure 3.3.4: Parallel Resistance of Circular Device .....                                    | 116 |

| Figure 3.3.5: Channel Length Modulation Analysis.....                                         | 117 |

| Figure 3.3.6: Channel Length Modulation Example .....                                         | 117 |

|                                                                                                                                                  |     |

|--------------------------------------------------------------------------------------------------------------------------------------------------|-----|

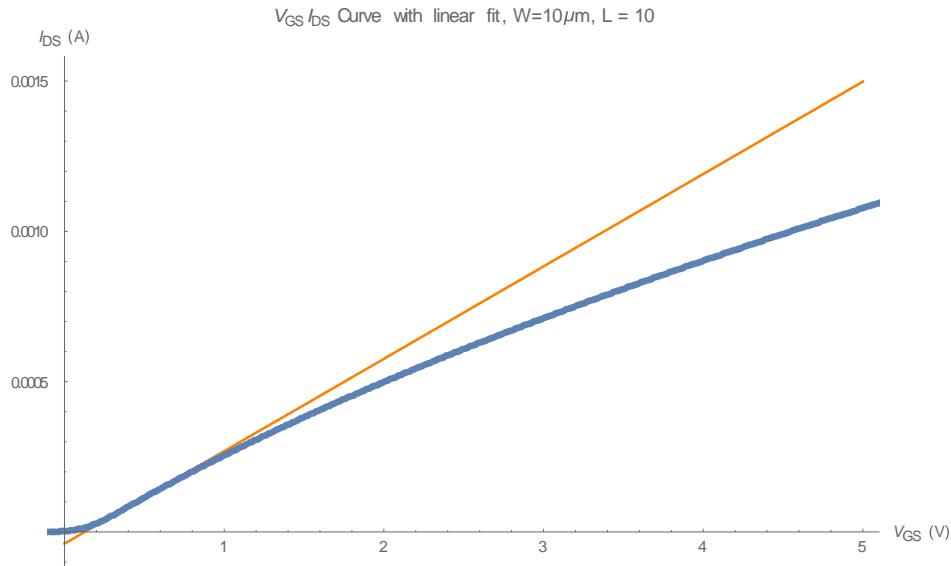

| Figure 3.3.7: VGSIDS of W:10 W/L:10 .....                                                                                                        | 118 |

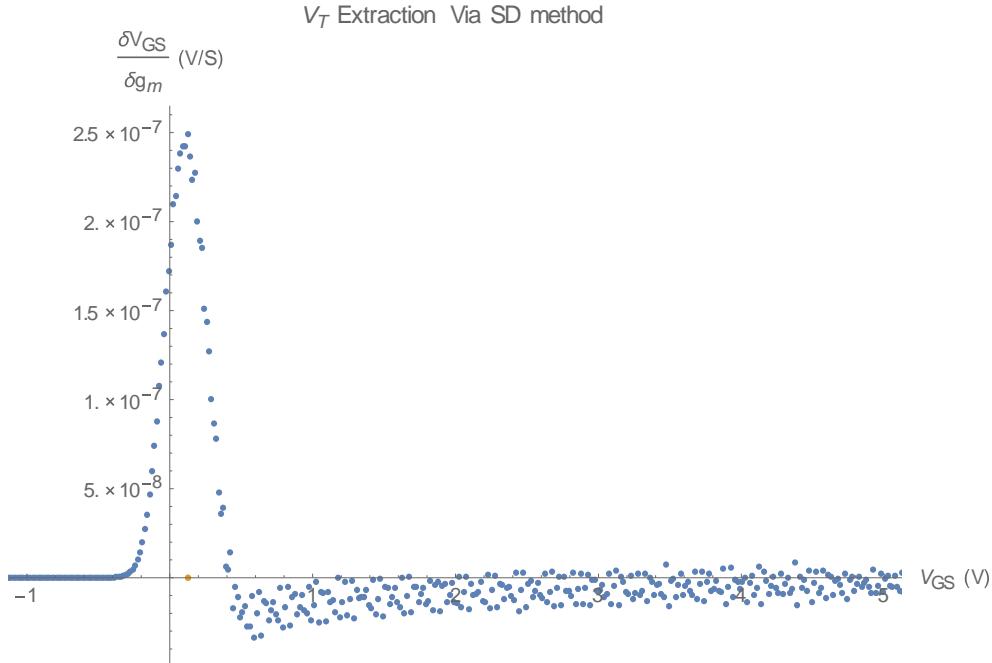

| Figure 3.3.8 SD method extraction .....                                                                                                          | 119 |

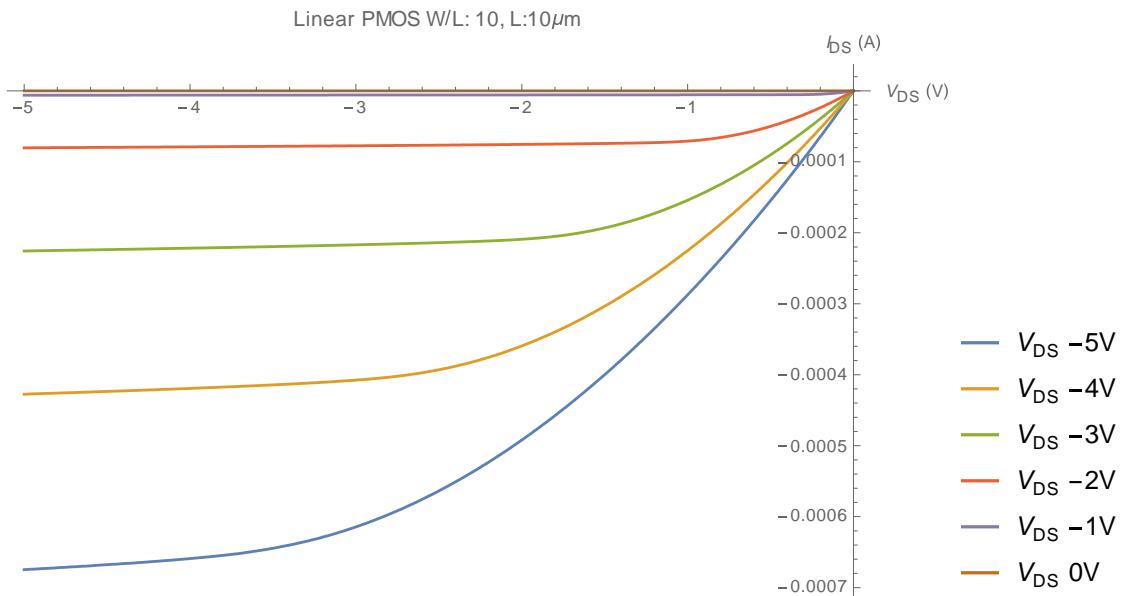

| Figure 3.4.1: Linear PMOS $V_{DS}I_{DS}$ .....                                                                                                   | 120 |

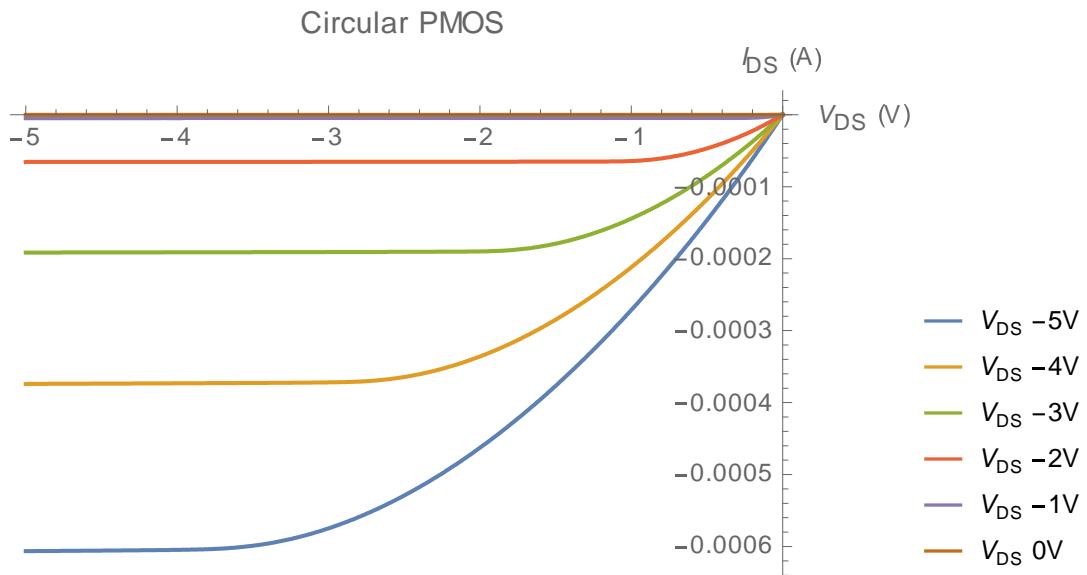

| Figure 3.4.2 Circular PMOS $V_{DS}I_{DS}$ .....                                                                                                  | 121 |

| Figure 3.4.3 Parallel resistance in PMOS .....                                                                                                   | 121 |

| Figure 3.4.4 Expanded Linear MOS W/L 10 L 10 $\mu$ m $V_{DS}=0$ .....                                                                            | 122 |

| Figure 3.4.5 $\lambda$ values of PMOS.....                                                                                                       | 122 |

| Figure 3.4.6: $\lambda$ slope on W/L 10 L10 $\mu$ m PMOS .....                                                                                   | 123 |

| Figure 3.4.7 ELR extraction on PMOS.....                                                                                                         | 123 |

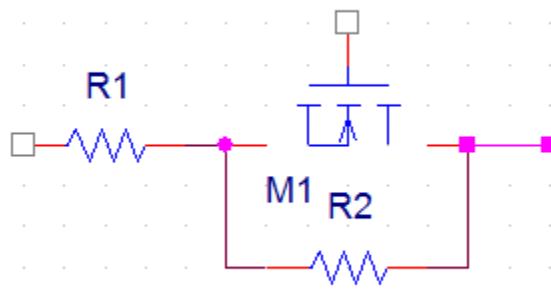

| Figure 3.5.1 Model Effective Circuit.....                                                                                                        | 125 |

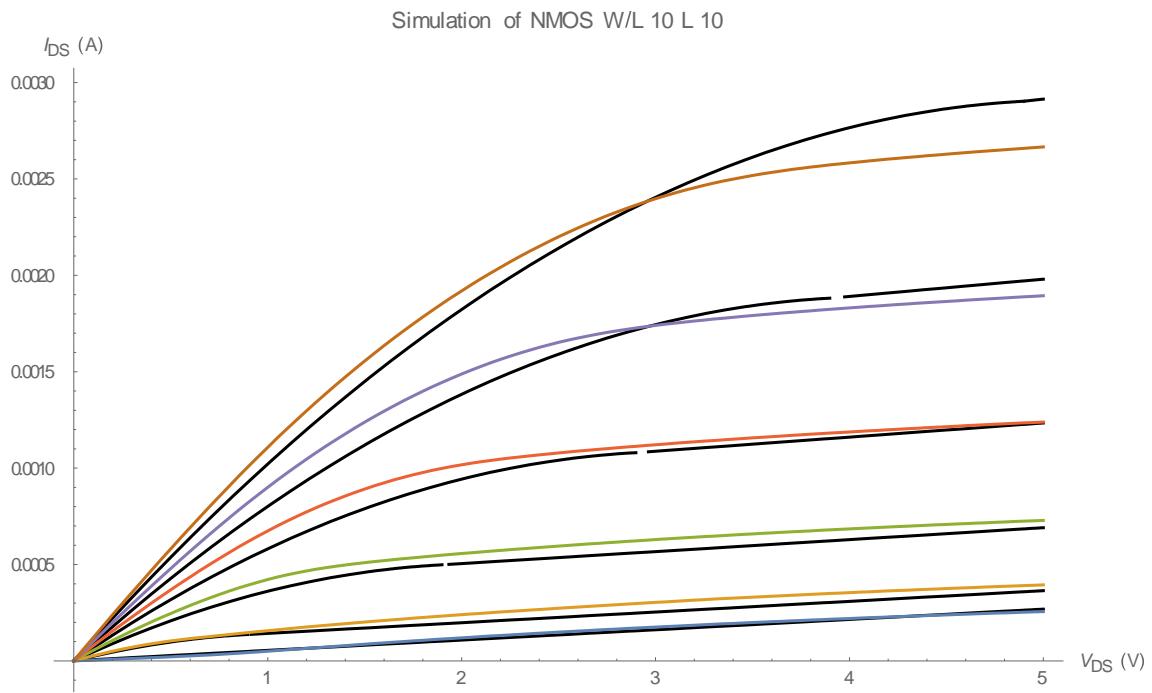

| Figure 3.5.2 Simulation of NMOS comparison .....                                                                                                 | 125 |

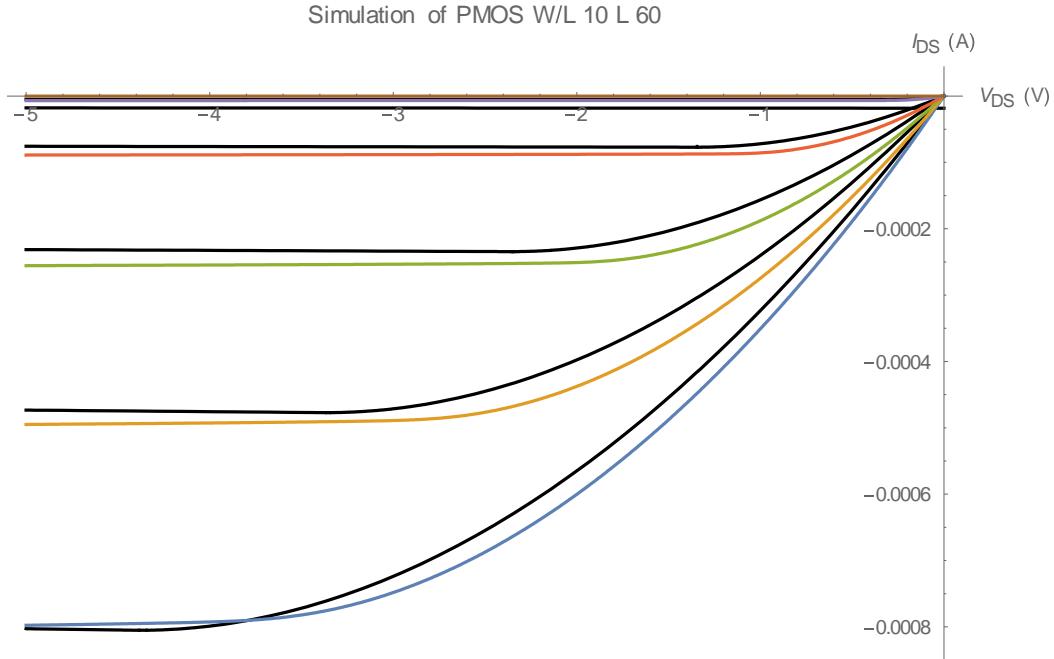

| Figure 3.5.3 Simulation of PMOS comparison.....                                                                                                  | 126 |

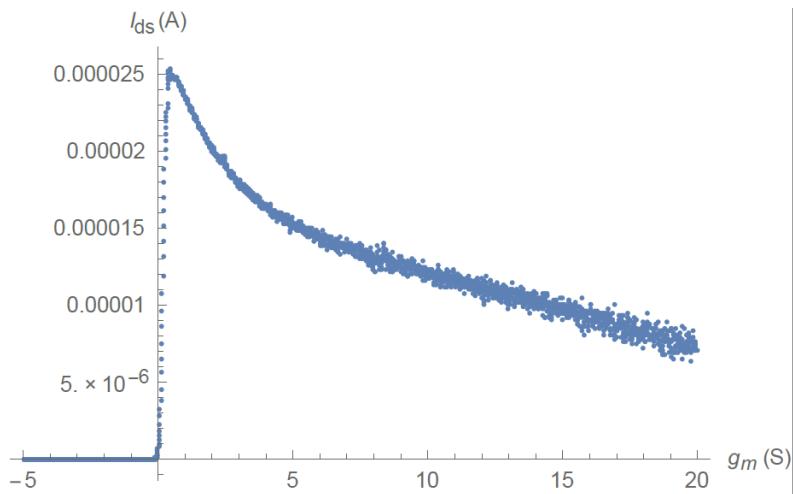

| Figure 3.7.1 Transconductance vs $I_{DS}$ for linear nMOS of W/L ratio 10 .....                                                                  | 127 |

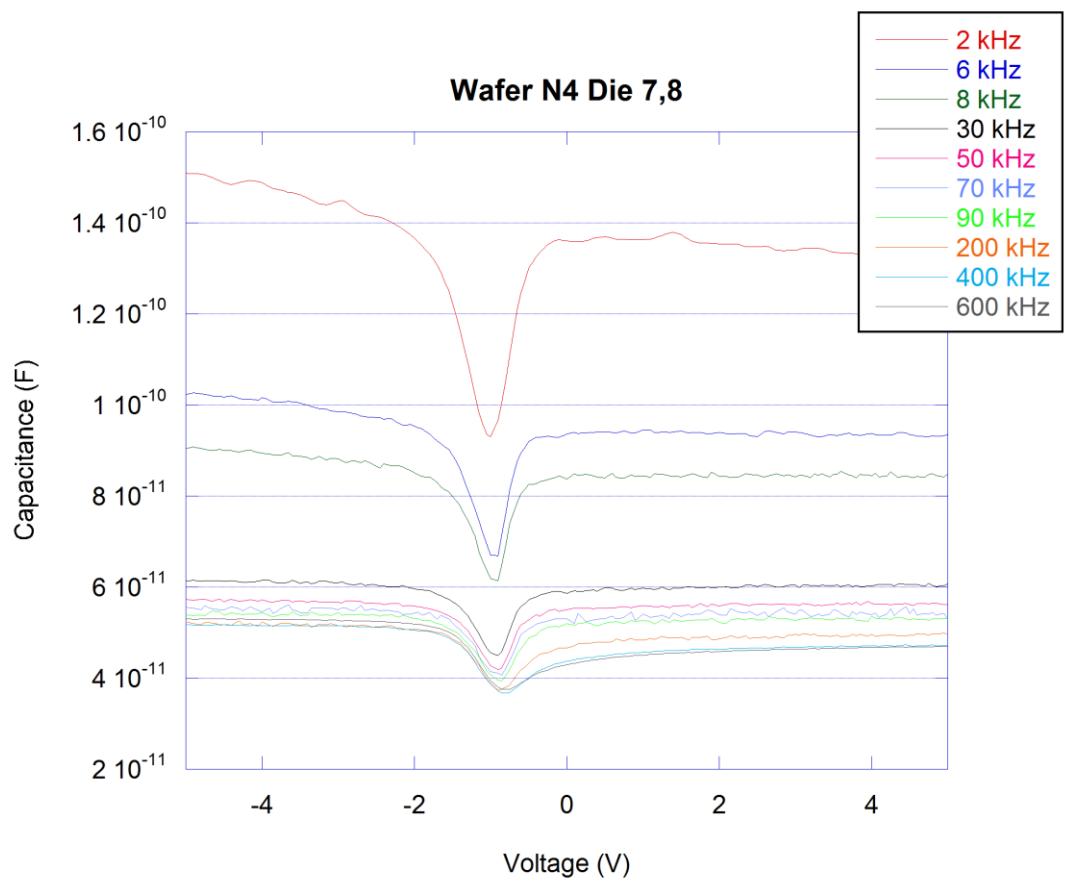

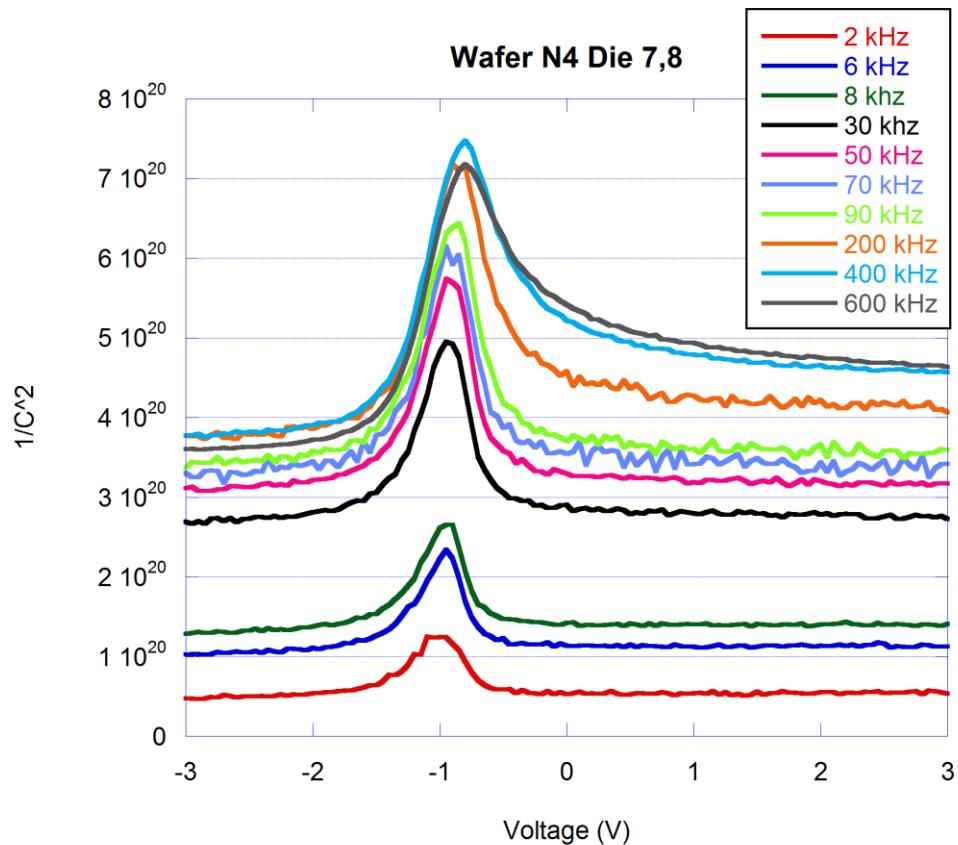

| Figure 3.8.1 CV Wafer N4 Die 7,8 .....                                                                                                           | 134 |

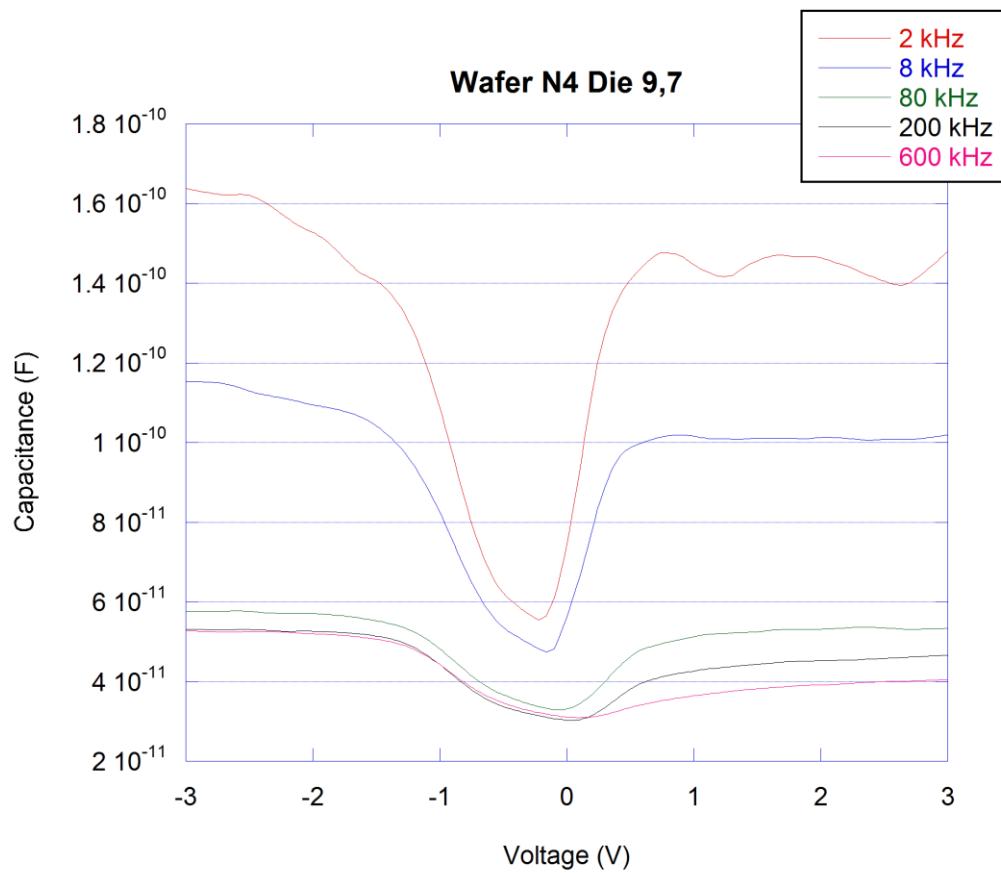

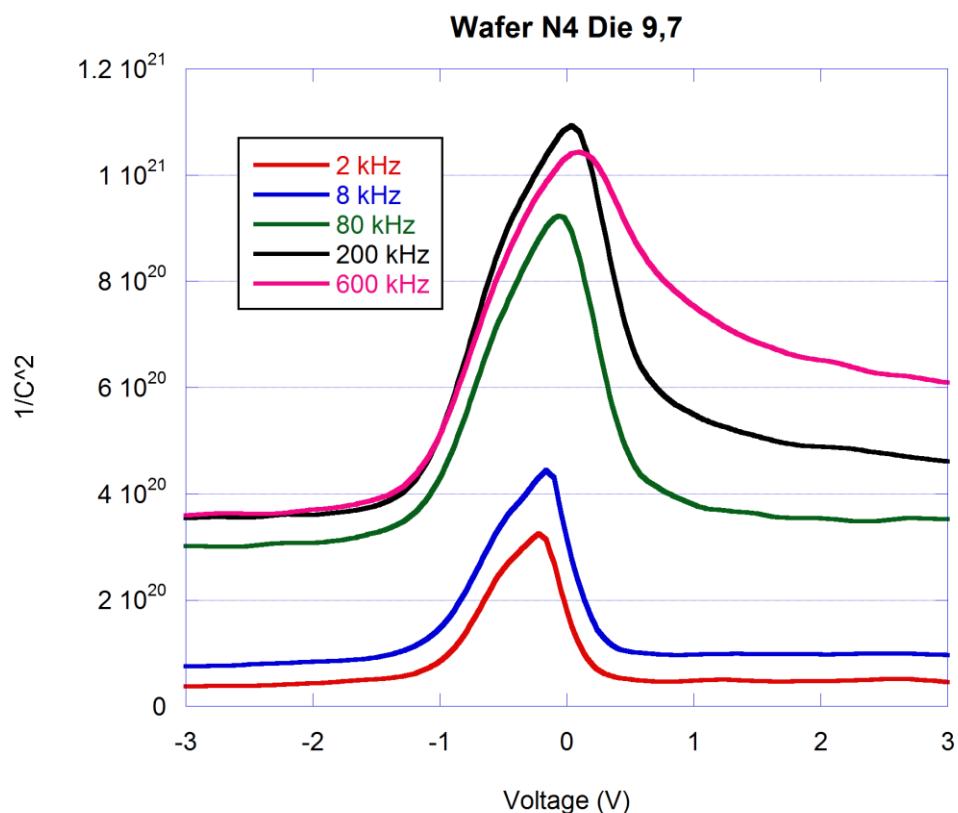

| Figure 3.8.2 CV Wafer N4 Die 9,7 .....                                                                                                           | 135 |

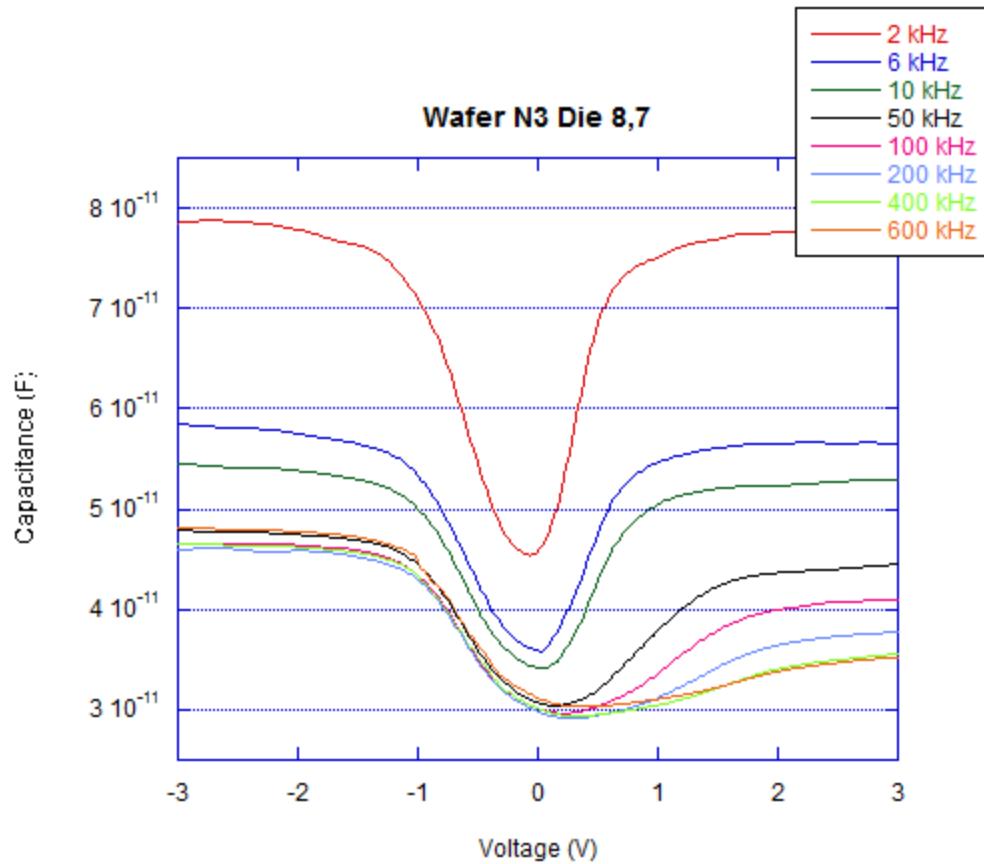

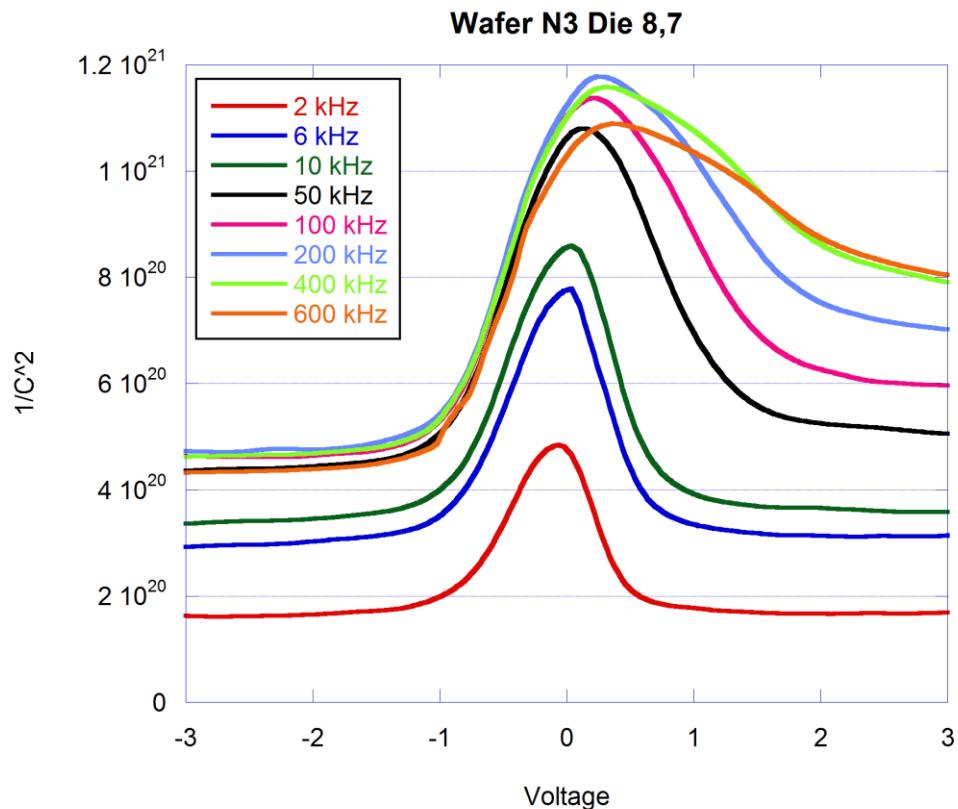

| Figure 3.8.3 CV Wafer N3 Die 8,7 .....                                                                                                           | 136 |

| Figure 3.8.4 $1/C^2$ Wafer N4 Die 7,8 .....                                                                                                      | 138 |

| Figure 3.8.5 $1/C^2$ Wafer N4 Die 9,7 .....                                                                                                      | 139 |

| Figure 3.8.6 $1/C^2$ Wafer N3 Die 8,7 .....                                                                                                      | 140 |

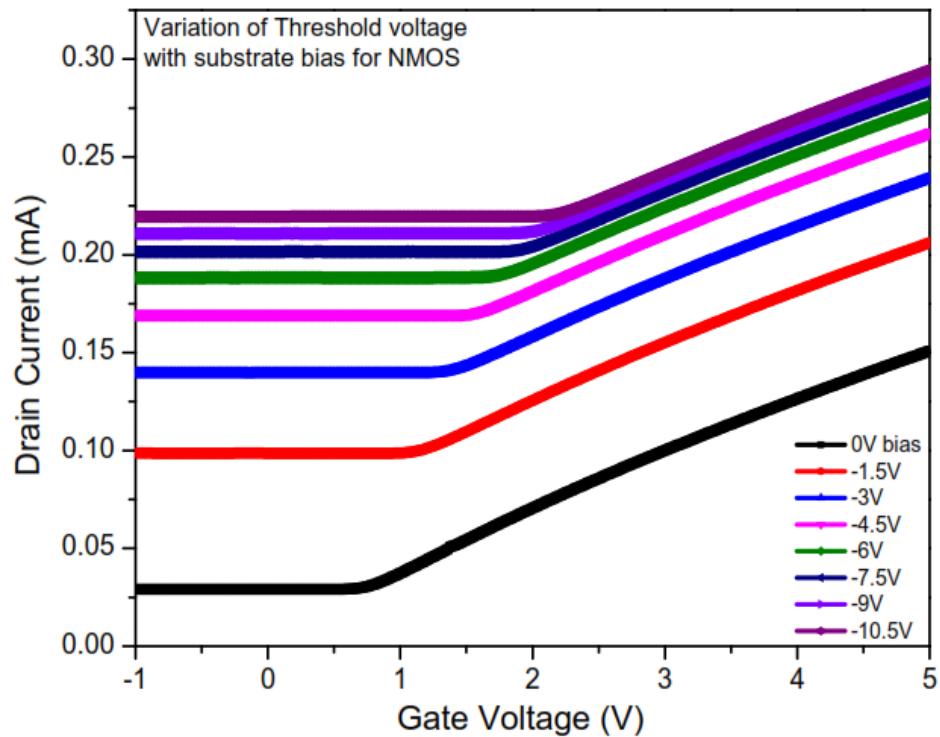

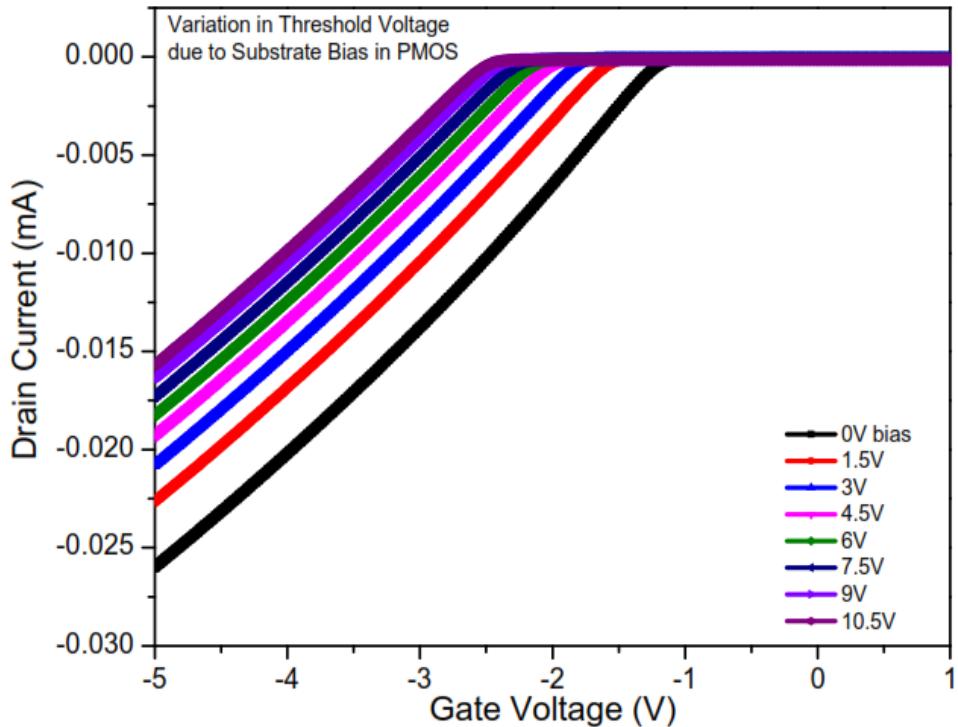

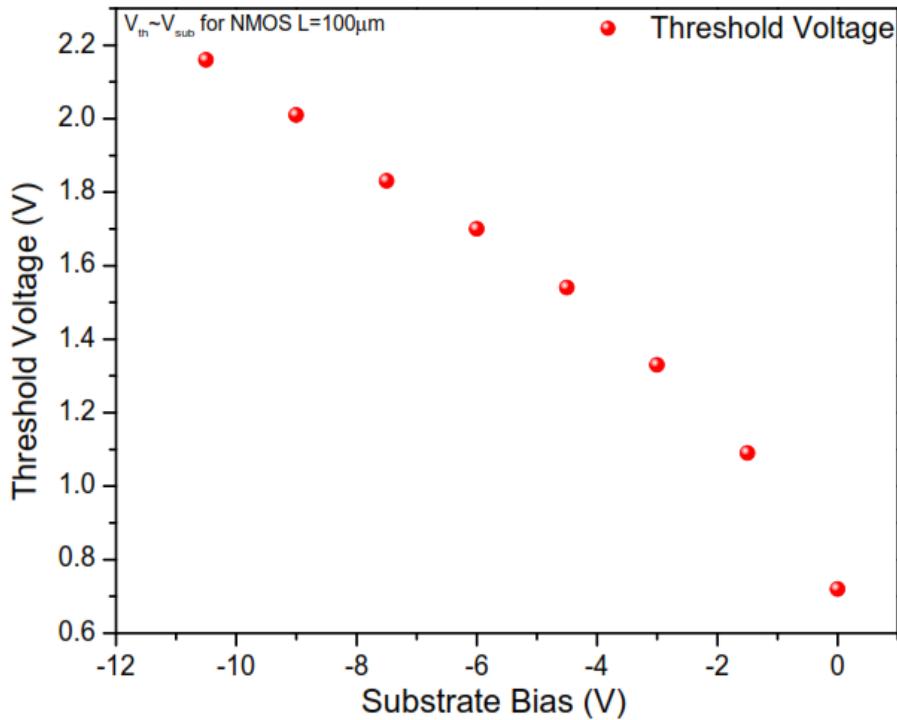

| Figure 3.9.1 $I_D \sim V_G$ Characteristics for a linear NMOSFET of 100 $\mu$ m length under various substrate bias voltages (0 to -10.5 V)..... | 142 |

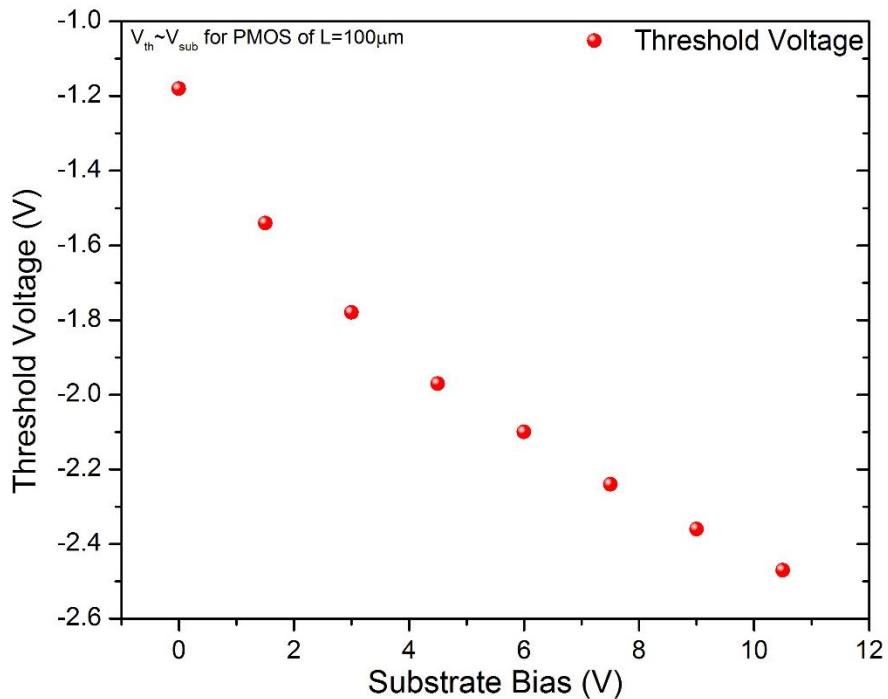

| Figure 3.9.2 $I_D \sim V_G$ Characteristics for a linear PMOSFET of 100 $\mu$ m length under various substrate bias voltages (0 to 10.5 V).....  | 143 |

|                                                                                                                                                                                                                                                                                                                                |     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 3.9.3 Threshold voltage as a function of substrate bias for linear NMOS of channel length L=100 $\mu$ m.....                                                                                                                                                                                                            | 144 |

| Figure 3.9.4 Threshold voltage as a function of substrate bias for linear PMOS of channel length L=100 $\mu$ m.....                                                                                                                                                                                                            | 144 |

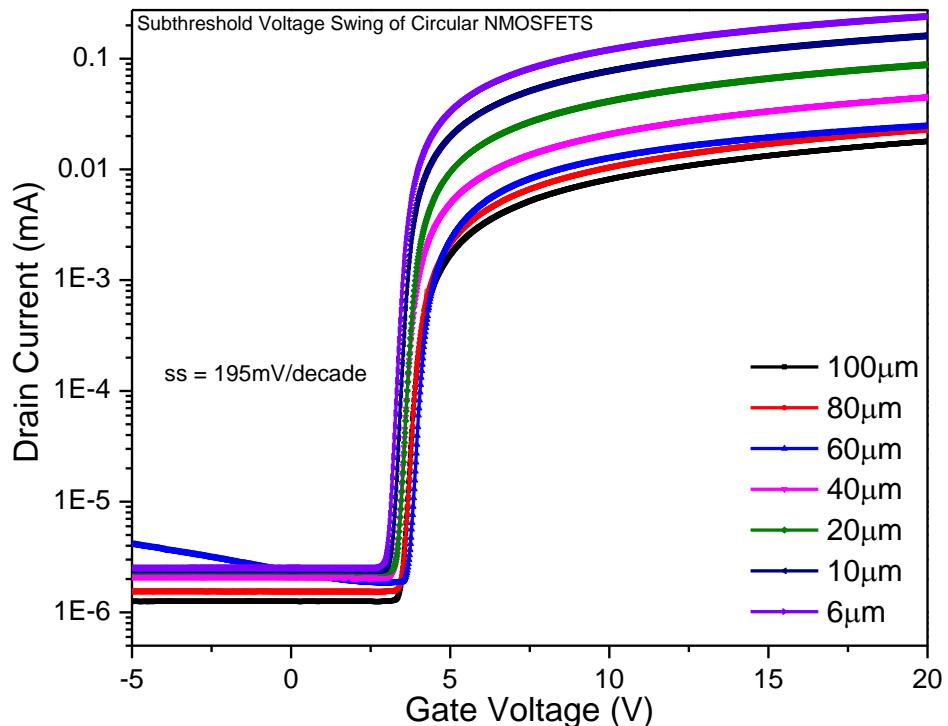

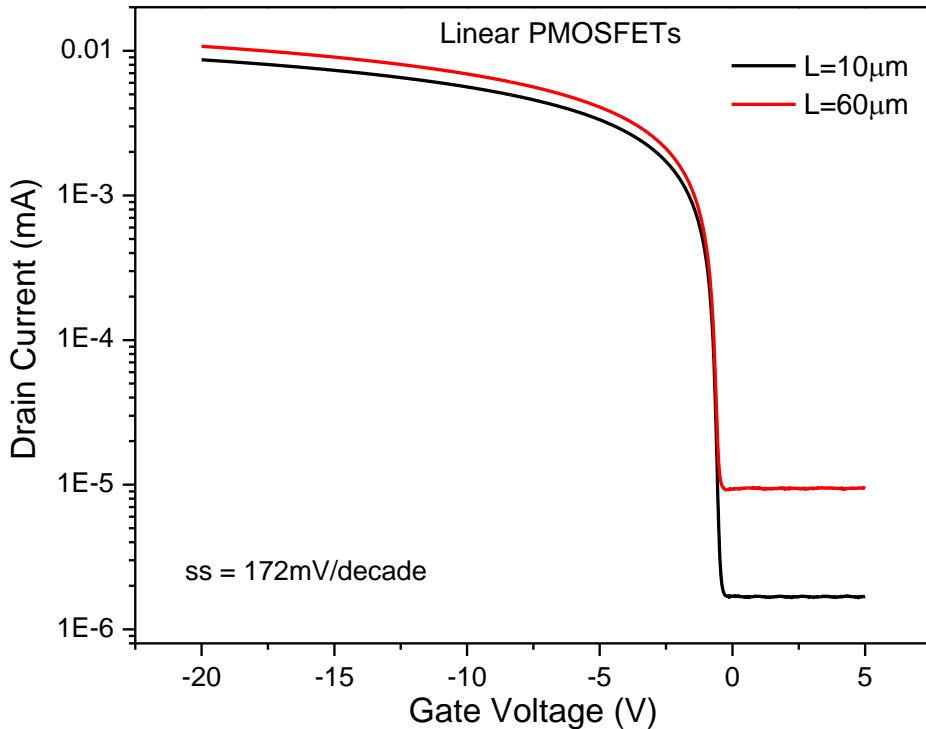

| Figure 3.10.1 log (I <sub>DS</sub> )-V <sub>GS</sub> characteristics to determine the sub-threshold voltage swing of circular NMOSFETs of different channel lengths.....                                                                                                                                                       | 145 |

| Figure 3.10.2 log (I <sub>DS</sub> )-V <sub>GS</sub> characteristics to determine the sub-threshold voltage swing of linear PMOSFETs of different channel lengths.....                                                                                                                                                         | 146 |

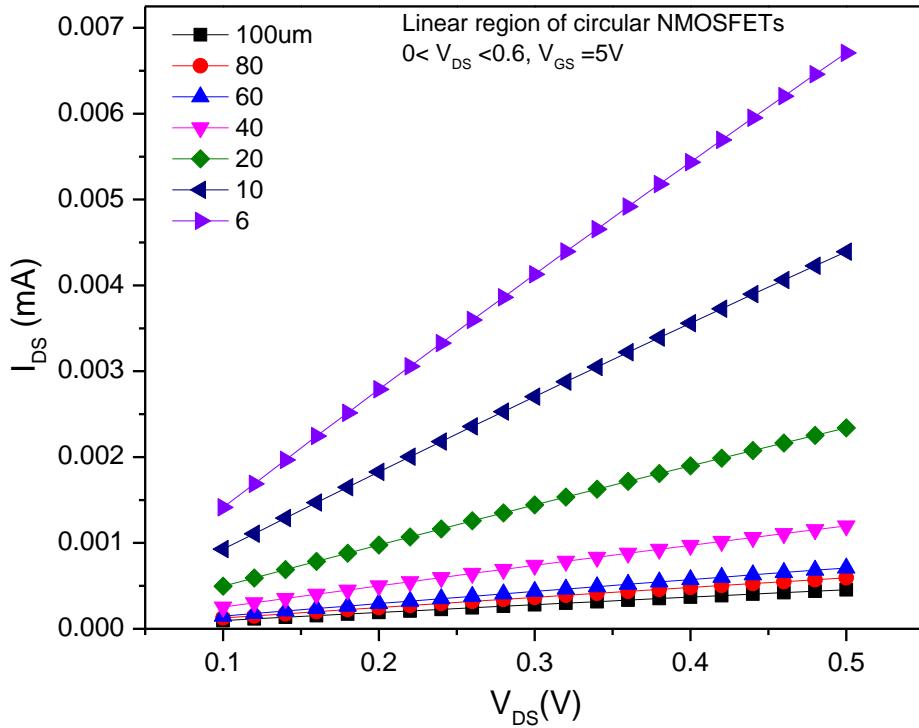

| Figure 3.11.1 I <sub>DS</sub> -V <sub>DS</sub> characteristics of circular NMOSFETs of different channel lengths in linear region (0.1V<=V <sub>DS</sub> <=0.5V) at V <sub>GS</sub> = 5V.....                                                                                                                                  | 147 |

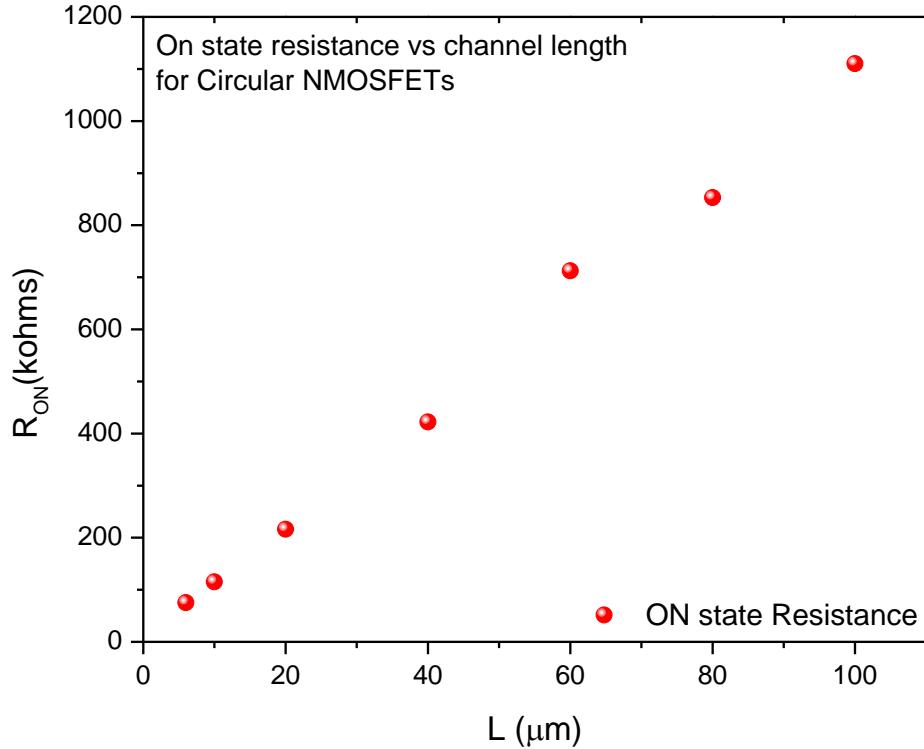

| Figure 3.11.2 R <sub>ON</sub> vs. L plot of circular NMOSFETs for different channel lengths in linear region (0.1V<=V <sub>DS</sub> <=0.5V) at V <sub>GS</sub> = 5V.....                                                                                                                                                       | 148 |

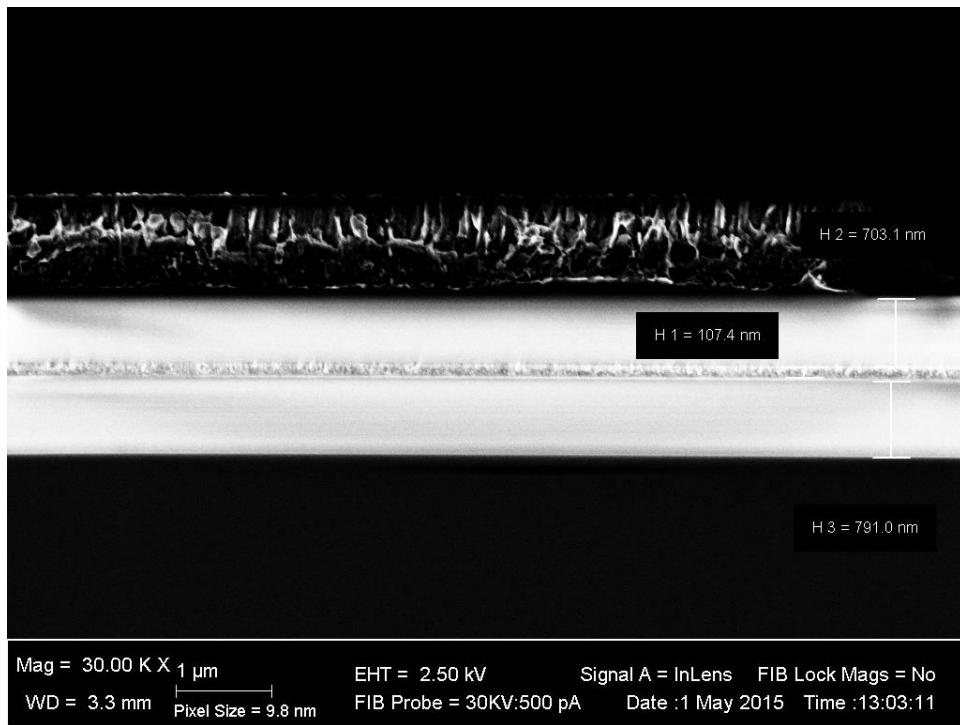

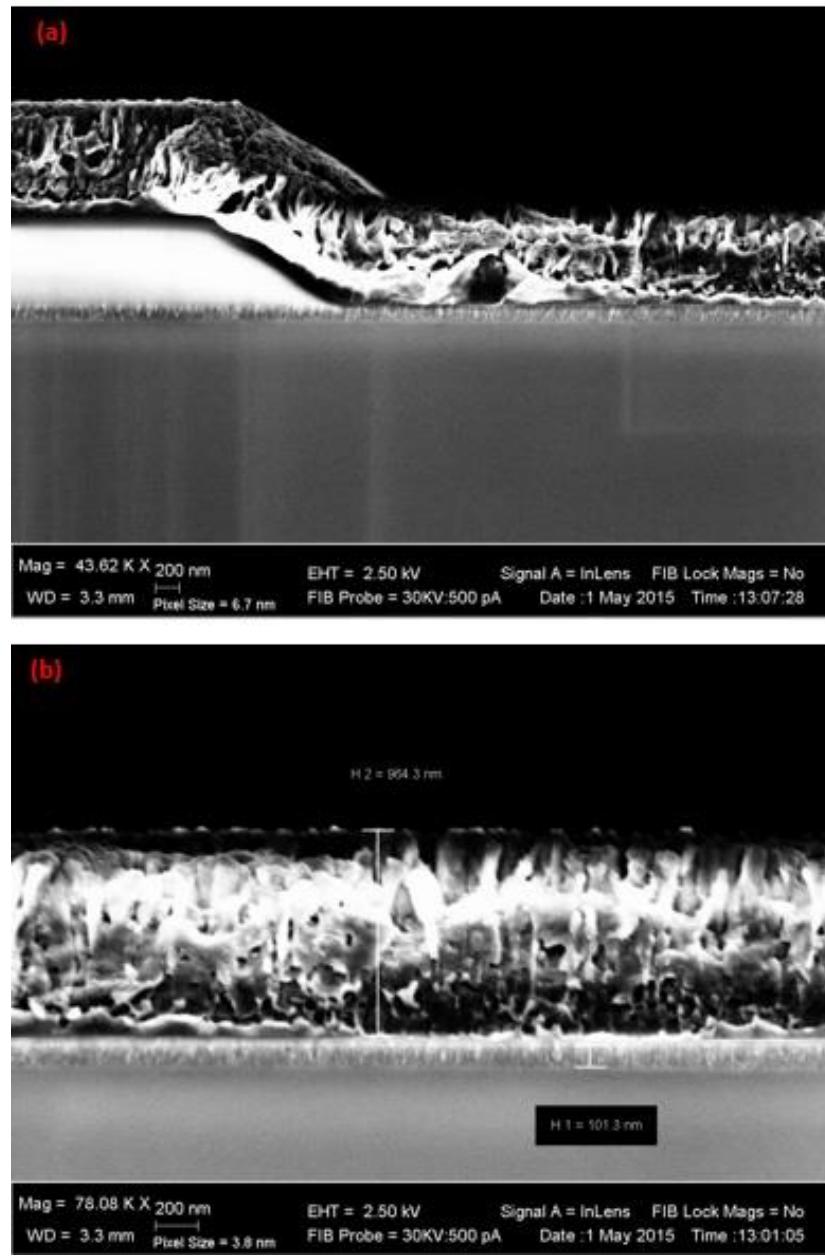

| Figure 3.12.1 SEM image of the Cross-section of a linear PMOSFET with thickness of various layers indicated- ~703nm ILD oxide layer, ~107nm thick Si <sub>3</sub> N <sub>4</sub> on top of ~791nm oxide layer.....                                                                                                             | 149 |

| Figure 3.12.2 SEM images of the Cross-section of a linear PMOSFET (a) showing the S/D region on the right with a continuous Si <sub>3</sub> N <sub>4</sub> layer underneath, (b) a magnified image of the S/D region with ~964nm thick Al electrode on top of un-etched ~101nm thick Si <sub>3</sub> N <sub>4</sub> layer..... | 151 |

# Table of Tables

|                                                                                 |     |

|---------------------------------------------------------------------------------|-----|

| Table 1.3.1 Clean room rating by air purity.....                                | 36  |

| Table 1.3.2 Linear and Parabolic rate constants for dry and wet oxidation.....  | 39  |

| Table 1.3.3 Bulk resistivity of commonly used metals.....                       | 49  |

| Table 2.1.1 RCA clean procedure.....                                            | 87  |

| Table 2.1.2 Detailed procedure for field oxide growth.....                      | 90  |

| Table 2.2.1 Thickness measurement of field oxide (unit: nm) .....               | 92  |

| Table 2.3.1 Detailed procedure for gate oxide growth. ....                      | 97  |

| Table 2.3.2 Recipe for poly-Si deposition .....                                 | 97  |

| Table 2.4.1 Recipe for RIE .....                                                | 99  |

| Table 2.5.1 Parameters used for PECVD on NMOS .....                             | 101 |

| Table 2.5.2 Recipe for $\text{Si}_3\text{N}_4$ deposition in a Plasmatherm..... | 101 |

| Table 2.5.3 Parameters used for ILD deposition on PMOS .....                    | 102 |

| Table 2.5.4 Recipe for ILD densification of NMOS. ....                          | 102 |

| Table 2.5.5 Recipe for ILD densification of PMOS. ....                          | 102 |

| Table 2.6.1Thickness of ILD layer after densification (unit: nm) .....          | 103 |

| Table 2.6.2 Procedure for ILD etching .....                                     | 104 |

| Table 3.1.1 Sheet resistance and Contact resistance results from TLM .....      | 111 |

| Table 3.1.2 Sheet resistance and Contact resistance results from TLM .....      | 112 |

| Table 3.2.1 Sheet resistance results fromVdP structure measurements.....        | 114 |

| Table 3.3.1: Extracted NMOS Values .....                                        | 119 |

| Table 3.4.1: PMOS Extracted Values .....                                        | 124 |

| Table 3.8.1 Oxide Thickness .....                                               | 136 |

| Table 3.8.2 Depletion Width.....                                                | 137 |

|                                                                                                                                                  |     |

|--------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Table 3.8.3 Threshold Voltage.....                                                                                                               | 138 |

| Table 3.8.4 Dopant Concentration .....                                                                                                           | 140 |

| Table 3.8.5 Fixed Oxide Charge .....                                                                                                             | 141 |

| Table 3.11.1Table of $R_{ON}$ at different channel lengths calculated from linear region of circular<br>NMOSFET $I_{DS}$ vs. $V_{GS}$ plot. .... | 148 |

## **Acknowledgment**

First and foremost, we would like to thank Prof. Chow for giving us the opportunity to take the Integrated Circuit Fabrication Laboratory. We are grateful for Prof. Chow's effort to bridge the theory of IC fabrication and its actual fabrication processes in the clean room, which in turn helps us achieve a better understanding of semiconductor device physics.

We would like to give a huge thanks to the clean room staff, Bryant Colwill, Kent Way for their guidance and assistance in the IC fabrication process throughout the semester. We learn a great deal from them, which we could never learn from the textbook. A special thanks goes to Zonghuan Lu, who helped us with SEM imaging for failure analysis.

Many thanks go to the teaching assistant, Peng-Yu Su, for his hard work and his help during the fabrication and testing processes.

## Abstract

In this Integrated Circuit (IC) Fabrication Laboratory course, we learned the fundamentals of IC fabrication and gained extensive experience in fabricating various types of devices on silicon wafers. In order to fabricate the N-MOS and P-MOS, multiple techniques, including thermal oxidation, photolithography, chemical vapor deposition (CVD), physical vapor deposition (PVD), reactive ion etching (RIE) and ion implantation, were applied during the fabrication process. Film thickness measurements were performed throughout the entire process to ensure that the actual thickness of different layers were within the acceptable error range with respect to the target. The IC fabrication process was also simulated with TSUPREM simulation and the results were compared with our experimental results.

Upon completion of the device fabrication, electrical tests were performed on different types of devices. Current-voltage characteristics were obtained for circular field effect transistors (FETs) and linear FETs on both N-MOS and P-MOS. Leakage current, threshold voltage, transconductance, channel conductance were determined from I-V characteristics. Capacitance-voltage measurements were taken for MOS capacitors. In addition, sheet resistance of source-drain area and contact resistance between metal, source and drain were obtained by characterizing the transmission lines, Kelvin structure, and van der Pauw structure.

## Team Responsibility

| Group Member       | Characterization Responsibilities                                                                                                                                                  | Report Contribution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Omotoyosi Taiwo    | Transmissionn Lines, Kelvin Structures and Van der Pauw structures for all PMOS and NMOS wafers                                                                                    | <ul style="list-style-type: none"> <li>-All processing steps (photolithography, etching...)</li> <li>-Transconductance explanation</li> <li>-Contact resistance and Sheet resistance (NMOS,PMOS)</li> <li>-Results from Resistance structure tests</li> <li>-Conclusion All resistance structures</li> </ul>                                                                                                                                                                                                                     |

| Dibyajyoti Mohanty | <ul style="list-style-type: none"> <li>-C-V characteristics (Both PMOS and NMOS wafers)</li> <li>-Substrate biasing of PMOSFET and NMOSFETs</li> <li>-Process Modelling</li> </ul> | <ul style="list-style-type: none"> <li>-Device Physics</li> <li>--MOS capacitors,</li> <li>--C-V characteristics</li> <li>--<math>I_D - V_D</math> and <math>I_D - V_G</math> Characteristics</li> <li>-Process Modelling and Simulation for PMOS and NMOS</li> <li>-Electrical Testing</li> <li>--Effect of substrate biasing</li> <li>--On state resistance</li> <li>-- Subthreshold swing</li> <li>--C-V measurement of PMOS</li> <li>-Failure Analysis of PMOS wafers</li> <li>-Conclusion (C-V characterization)</li> </ul> |

|                 |                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                          |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Tyler Mason     | -CV characteristics                                                                                                                                                                          | <ul style="list-style-type: none"> <li>-Introduction</li> <li>-Introduction to MOSFETs</li> <li>-Transfer Characteristice</li> <li>-Non-ideal MOSFETs</li> <li>-CV Measurements characterization</li> <li>-CV Measurements of NMOS</li> <li>-Conclusion (CV characterization)</li> </ul> |

| Fengyuan Lai    | <ul style="list-style-type: none"> <li>-I-V characteristics for both NMOS and PMOS</li> <li>-Substrate biasing for NMOSFET and PMOSFET</li> </ul>                                            | <ul style="list-style-type: none"> <li>-Abstract and acknowledgment</li> <li>-I-V characteristics</li> <li>-Detailed processing procedures</li> <li>-Conclusion</li> <li>-Report compilation</li> </ul>                                                                                  |

| Seth Lowenstern | <ul style="list-style-type: none"> <li>-IV characteristics of PMOS and NMOS, including <math>V_{GS}I_{DS}</math>, <math>V_{DS}I_{DS}</math>, and extracting parameters</li> <li>-</li> </ul> | <ul style="list-style-type: none"> <li>-Current-Voltage Measurements, NMOS and PMOS</li> <li>-Parallel resistance extraction</li> <li>-Channel Length Modulation</li> <li>-Threshold Voltage</li> <li>-Mathematical device Modeling</li> </ul>                                           |

## 1. Technical Background

### 1.1 Introduction

An integrated circuit, also referred to as an IC, is a collection of electric devices fabricated on a piece of semiconductor material, most commonly silicon. The integrated circuit was first patented by Jack Kilby on February 6, 1959 while employed by Texas Instruments. The IC was an important step forward because it allowed for the miniaturization of electronic components, the most important of which was the transistor.

The first patent for a field effect transistor was filed by Julius Lilienfeld in 1925. Lilienfeld did not publish any research supporting the claims in his patent, nor did he have a working prototype, so his work went ignored until 1947. In 1947, Shockley, Bardeen, and Brattain produced the first practical transistor while working at AT&T's Bell Labs. In 1956 they received the Nobel Prize in Physics for their work "... on semiconductors and their discovery of the transistor effect." In 1960, four years after Shockley, Bardeen, and Brattain won the Nobel Prize, Kahng and Atalla produced the first metal oxide semiconductor field effect transistor, or MOSFET. Transistors replaced vacuum tubes as they are much sturdier, much smaller, and are cheaper and easier to produce on a mass scale.

A transistor itself is an interesting electronic device with applications in signal amplification and binary information switches. This second property makes transistors the basis of modern computing devices. Transistors are capable of these applications because of their unique behavior. A typical MOSFET has three terminals, referred to as the source, gate, and drain. The voltage applied to the gate controls the current between the source and drain, so when no voltage is applied to the gate, there is no current across the source and drain, similar to an open switch. When voltage is applied to the gate current flows and the system behaves as if an open switch had been closed. For lower gate voltages the system shows linear behavior, where the source drain current increases linearly with the gate voltage, which allows the transistor to be used as a signal amplifier.

There is always demand for smaller, more reliable, more efficient electrical devices, which makes the production of integrated circuits, and MOSFETs in particular, is an important topic of study, especially for industry application. In this paper we discuss the production of an integrated circuit on a silicon wafer. The devices fabricated include rectangular MOSFETs, circular MOSFETs, several resistance test structures, and MOS capacitors. These structures were fabricated through the use of multiple techniques, including chemical vapor deposition, physical vapor deposition, photolithography, plasma etching, wet etching, and ion implantation.

In Chapter 1 of this report the theoretical background of the behavior, processing, and testing of IC devices is laid out. In Chapter 2 the actual processes used to fabricate the ICs are described. In Chapter 3 the method by which the devices are tested, and the results of those tests are presented. Chapter 4 compares the results of the actual devices to the behavior of a simulated IC and discusses the differences between ideal and real behavior of the devices.

## 1.2 Device Physics

### 1.2.1 Introduction to MOSFET

A metal oxide semiconductor field effect transistor, or MOSFET, is one of the most common devices fabricated as part of an integrated circuit. The transistor is so useful because it allows for the electronic amplification or switching of signals, the second property making it the basis of digital electronics designs.

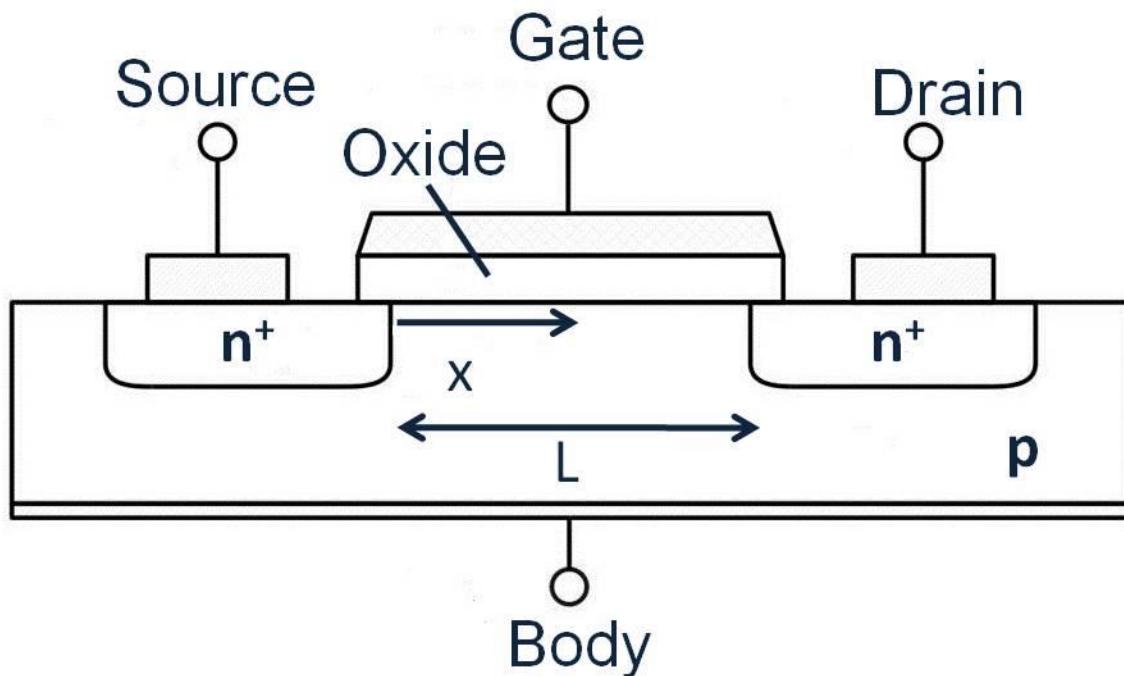

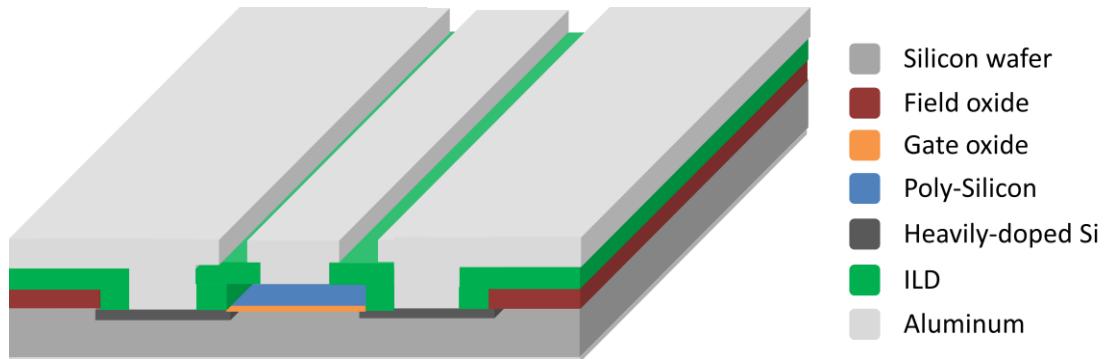

A MOSFET can either be n-type or p-type, depending on the type of dopant used to create the source and drain terminals. For an n-type MOSFET the device is fabricated on a p doped substrate. The source and drain terminals are created by highly doping the substrate with an n+ dopant. A thin layer of oxide and a layer of metal, for our devices a layer of polysilicon, are fabricated on top of the space between the n+ doped areas, creating the gate terminal. A cross section of a MOSFET is shown in the illustration below.

Figure 1.2.1 MOSFET Cross-Section

The MOSFET is operated by the application of a voltage to the gate terminal. The metal and the substrate act as the plates in a parallel plate capacitor, with the oxide being a dielectric medium separating the two plates. Applying a positive voltage to the gate terminal, relative to the substrate, causes the build up of negative charges in the substrate near the oxide-substrate boundary. These negative charges come in the form of a depletion layer and an inversion layer of mobile electrons. The mobile electron layer forms a channel that allows current to flow between the source and drain terminals. The voltage applied to the gate required to form the conducting channel is known as the threshold voltage, and it is an important characteristic value of a MOSFET. The threshold voltage can be controlled in the ideal case by factors such as oxide thickness and substrate dopant concentration. The threshold voltage can also be affected by non-ideal effects due to fabrication methods.

### 1.2.2 Different Types of Field-Effect Transistors

### 1.2.3 Basic Device Characteristics

### 1.2.4 MOS Structure

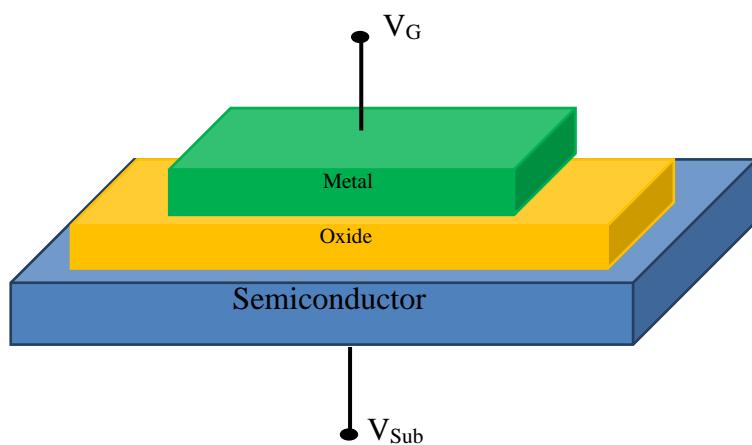

Metal Oxide Semiconductor (MOS) structure consists of a layer of insulating oxide layer sandwiched between metal and semiconductor, that's why it is also Metal Insulator Semiconductor (MIS) structure. It behaves like a parallel plate capacitor, with the oxide layer working as a dielectric layer and the terminals being the metal and semiconductor. When bias is applied to the top metal terminal, it produces an electric field, which results in collection of charge carriers (majority or minority depending on the polarity of bias) at the semiconductor and oxide interface.

**Figure 1.2.2 Metal Oxide Semiconductor (MOS) Capacitor structure- Oxide layer sandwiched between metal and semiconductor layers.**

### 1.2.4.1 Energy Band Diagram of MOS Capacitors

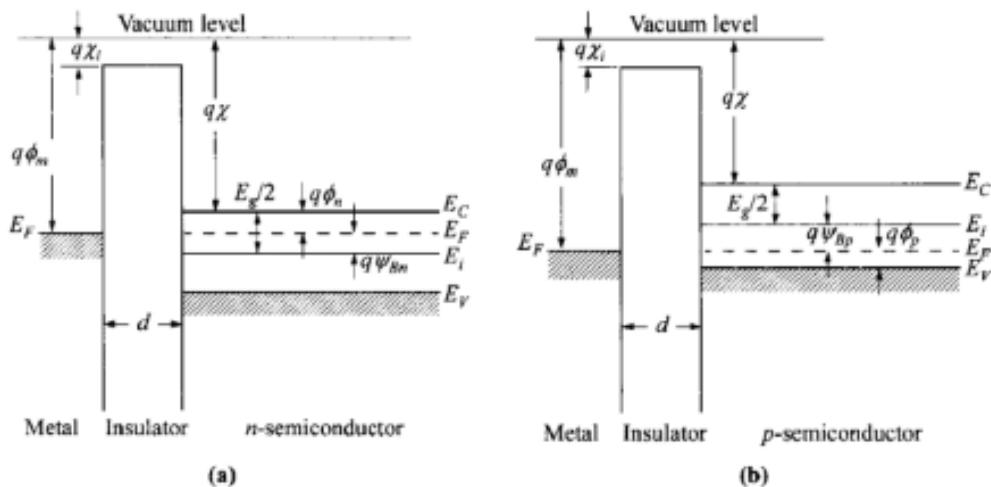

Energy band diagram is used to study carrier behavior at different biasing condition in a semiconductor. In an energy band diagram, the energy difference between Fermi level and Vacuum level is known as Work function ( $\phi$ ) and the energy difference between conduction band of the semiconductor and vacuum level is known as Electron affinity ( $\chi$ ). The work function of metal is denoted as  $\phi_m$  and that of semiconductor is  $\phi_s$ . If under zero bias condition the Fermi levels of semiconductor and metal are aligned with each other ( $\phi_m = \phi_s$ ), then it is called Flat Band condition. The behavior of MOS structure under different biasing conditions has been discussed below.

#### 1.2.4.1.1 Under zero bias condition ( $V_G=0$ )

The energy band diagram of ideal p- and n- MOS structures under zero bias condition is as shown in Figure 1.2.3. For our analysis, let us consider a p-type semiconductor MOS structure. As it is flat band condition ( $\phi_{ms} = \phi_m - \phi_s = 0$ ), the Fermi levels are perfectly aligned with each other and there is no charge flow in the structure.

**Figure 1.2.3 Energy band diagrams of ideal ( $\phi_{ms} = 0$ ) p- and n-MOS structure under zero bias condition [1].**

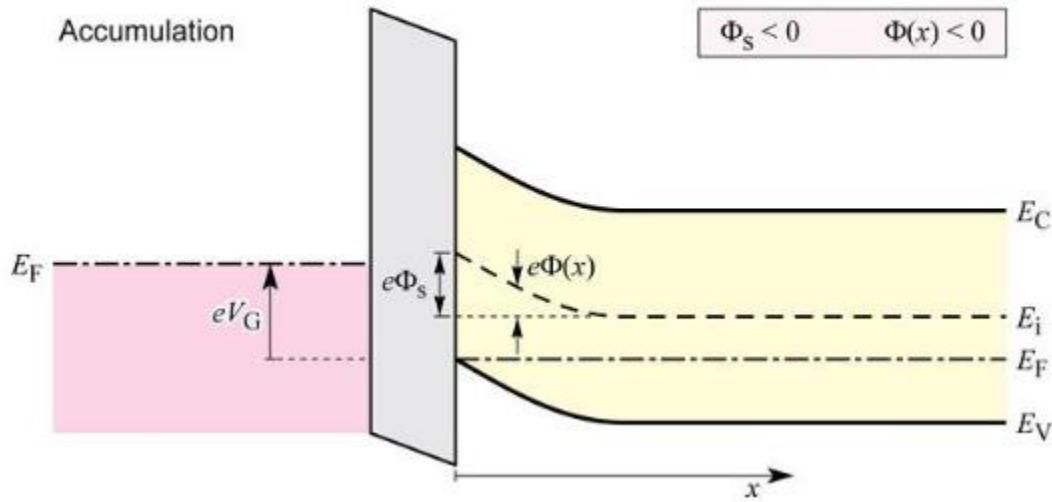

#### 1.2.4.1.2 Under negative bias condition ( $V_G < 0$ )

When a negative bias  $V < 0$  is applied to the metal with respect to the semiconductor, the metal becomes negatively charged and an equal amount of positive charge or hole accumulates at the semiconductor-oxide interface. This is known as accumulation condition and it results in a storage of majority carriers at the interface. Due to the application of this bias, Fermi level of metal ( $E_{Fm}$ ) moves above the semiconductor Fermi level ( $E_{Fs}$ ) by an amount  $qV$ . Due to this shift, band bending occurs as shown in the Figure 1.2.4.

**Figure 1.2.4 Band Structure of NMOS Capacitor in Accumulation condition where  $V_G < 0$  [2].**

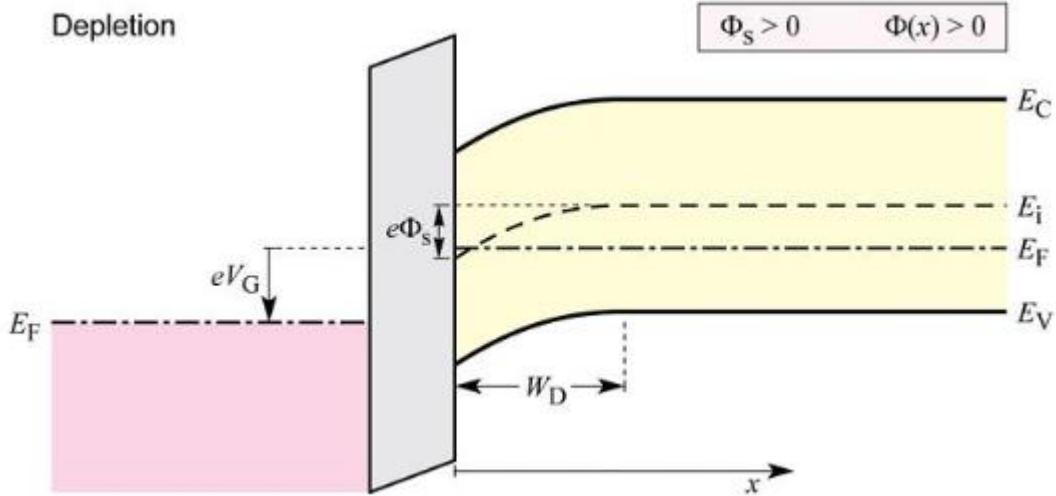

#### 1.2.4.1.3 Under small positive bias ( $V_T > V_G > 0$ )

When a small positive voltage is applied to the metal, it becomes positive with respect to the semiconductor, hence the accumulated holes at the interface are dispersed back into the bulk. This step is known as Depletion as it involves depletion of majority carriers from the interface. So in this stage the balancing negative charge at the interface is due to the immobile acceptor ions. Due to the positive potential applied to the metal, the Fermi level for metal,  $E_{Fm}$  shifts below  $E_{Fs}$  causing a band bending opposite to the previous step.

**Figure 1.2.5 Band Structure of NMOS Capacitor in Depletion regime, where applied voltage  $V_T > V_G > 0$  [2].**

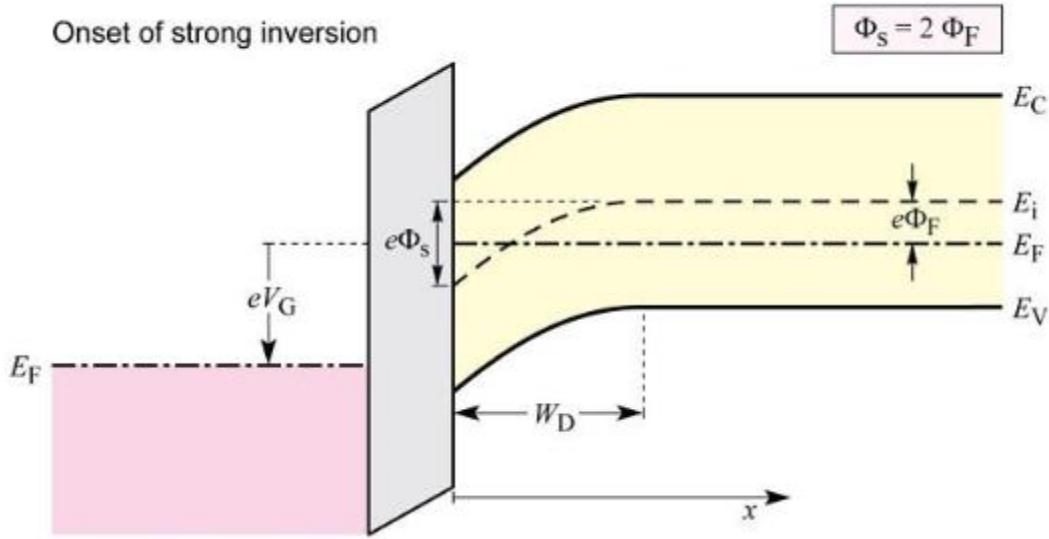

#### 1.2.4.1.4 Under large positive bias ( $V_G > V_T$ ):

When the positive bias applied to the metal electrode exceeds a certain voltage (known as Threshold Voltage  $V_{th}$ ), to compensate the positive charge, electrons start piling at the interface. As the minority carrier concentration accumulated at the interface exceeds that of majority acceptor ions, inversion is said to occur as shown in Figure 1.2.6. The intrinsic energy level ( $E_i$ ) bends further below the Fermi level. At Threshold voltage, onset of inversion is said to occur at which,

$$\varphi_s = 2\varphi_F = \frac{2(E_{i(bulk)} - E_F)}{q}$$

Where,  $\varphi_F$  is the electrostatic potential of Fermi level with respect to the intrinsic level for p-type substrate, given by

$$\varphi_F = \pm \frac{kT}{q} \ln \left( \frac{N_A}{n_i} \right)$$

**Figure 1.2.6 Band Structure of NMOS Capacitor at the onset of Strong Inversion regime with applied voltage to the metal electrode  $V_G = V_T$  [2].**

For n-type substrate, the negative sign is used with  $N_A$  replaced by  $N_D$ . If the voltage is increased way beyond threshold voltage, the depletion width doesn't change anymore. So the maximum depletion width for NMOS is given by,

$$W_{Dmax} = \sqrt{\frac{2\epsilon(2\varphi_F)}{qN_A}} = 2\sqrt{\frac{\epsilon kT}{q^2 N_A} \ln \frac{N_A}{n_i}}$$

The voltage drop across a MOS capacitor is given by,

$$V_G = V_{ox} + \varphi_s$$

Where,  $V_{ox}$  is the voltage drop across the oxide and  $\varphi_s$  is the surface potential of the semiconductor. So at the onset of strong inversion, when the voltage across the capacitor is the threshold voltage, the above equation becomes for an NMOS,

$$V_{th} = 2\varphi_F + \frac{\epsilon_s x_{ox}}{\epsilon_{ox}} \sqrt{\frac{4qN_A}{\epsilon_s \epsilon_0} \varphi_F}$$

The same equation for PMOS,

$$V_{th} = 2\varphi_F - \frac{\epsilon_s x_{ox}}{\epsilon_{ox}} \sqrt{\frac{4qN_D}{\epsilon_s \epsilon_0} (-\varphi_F)}$$

Surface potential  $\varphi_s$  can be used to define various biasing cases,

- 1)  $\varphi_s < 0$ , Accumulation of holes (Accumulation regime)

- 2)  $\varphi_s = 0$ , No band bending (Flat band condition)

- 3)  $\varphi_s > 0$ , Hole depletion from interface (Depletion regime)

- 4)  $2\varphi_F > \varphi_s > \varphi_F$ , electrons start piling at interface, (Weak inversion regime)

- 5)  $2\varphi_F \gg \varphi_s$ , electron inversion layer formed (Strong inversion regime)

The perpendicular electric field in depletion region is given by:

$$E_x = \frac{\sqrt{2}kT}{qL_D} \sqrt{\left[ \left( e^{\frac{-q\varphi_x}{kT}} + \frac{q\varphi_x}{kT} - 1 \right) + \frac{n_{p0}}{p_{p0}} \left( e^{\frac{q\varphi_x}{kT}} - \frac{q\varphi_x}{kT} - 1 \right) \right]}$$

Where,  $\varphi_x$  is the potential at any point at a distance  $x$  from the surface and  $L_D$  is the Debye screening length given by,

$$L_D = \sqrt{\frac{\epsilon_s kT}{q^2 p_{p0}}}$$

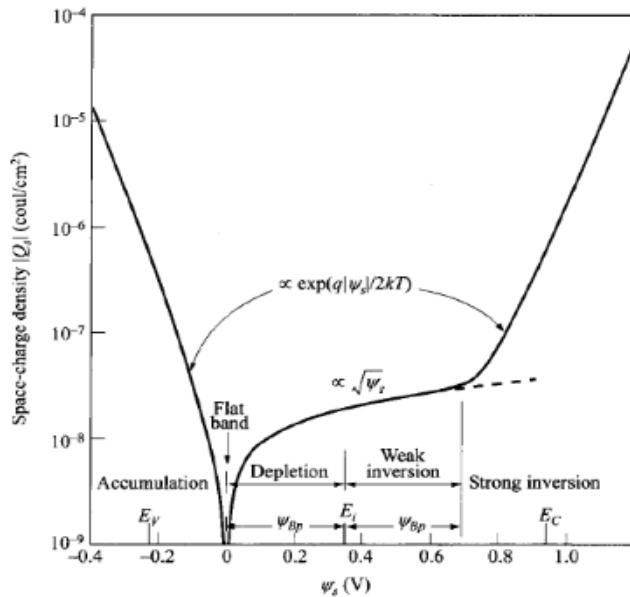

Using Gauss's law at the surface, charge stored at the surface can be determined by,  $Q_s = -\epsilon_s * E_s$ , where  $E_s$  is the electric field at the surface ( $x = 0$ ). The plot of  $Q_s$  in terms of surface potential  $\varphi_s$ , is given in Figure 1.2.7 below, which also shows the various bias regimes.

**Figure 1.2.7 Variation of surface charge density  $Q_s$  as a function of surface potential  $\psi_s$  for a p-type Si substrate with  $N_A = 4 \times 10^{15} \text{ cm}^{-3}$  [1].**

### 1.2.4.2 MOS Capacitance-Voltage (C-V) Characteristics:

The voltage applied across the MOS structure drops across it and is given by,

$$V_{MOS} = V_{OX} + \varphi_s$$

Where,  $V_{MOS}$  is the voltage applied across MOS,  $V_{OX}$  is the voltage drop across the oxide and  $\varphi_s$  is the surface potential of the semiconductor. The equivalent circuit for a MOS structure has two capacitors in series with each other- voltage independent oxide capacitance and voltage dependent depletion capacitance. There is variation in MOS capacitance depending on applied voltage and frequency is shown in Figure 1.2.8.

**Figure 1.2.8 Capacitance-Voltage characteristic of an NMOS with various bias regimes- accumulation, depletion, weak inversion, strong inversion and deep depletion indicated on the curve [1].**

#### 1.2.4.2.1 Accumulation Capacitance

In Accumulation regime ( $V_G < V_{FB}$ ), the negative voltage applied to the NMOS causes accumulation of holes at the interface. The high capacitance is close to the oxide capacitance. The oxide capacitance per unit area is given by,

$$C_i = \frac{\epsilon_{OX}}{d}$$

Where,  $d$  is the oxide thickness and  $\epsilon_{OX}$  is the oxide permittivity. It is denoted by  $C_i$  on the left hand side of Figure 1.2.8.

#### 1.2.4.2.2 Depletion Capacitance

When the voltage is increased beyond  $V_{FB}$ , and positive charge added to metal plate, repels the accumulated holes from semiconductor and oxide interface exposing the negatively charged acceptors. As the voltage is increased further, to compensate for the increasing positive voltage on the gate, the depletion layer thickness increases and holes from the interface are gradually removed. So the depletion regime capacitance is the series combination of oxide and depletion capacitances, which is given by,

$$C = \frac{C_i C_d}{C_i + C_d}$$

Where,  $C_d = \frac{\epsilon_s}{W}$  is the depletion capacitance.

#### 1.2.4.2.3 Inversion Capacitance

As the voltage is further increased and threshold voltage is reached, the charge on the surface of semiconductor changes from positive to negative and a layer of electrons get deposited. This inversion layer formation also results in maximum depletion layer width. Any further increase in gate voltage, doesn't cause subsequent increase in depletion layer width. Hence the capacitance in inversion region is the series combination of oxide capacitance with minimum depletion capacitance resulting from maximum depletion width. It is given by,

$$C = \frac{C_i C_{dmin}}{C_i + C_{dmin}}$$

Where,  $C_{dmin} = \frac{\epsilon_s}{W_{max}}$  is the minimum depletion capacitance.

#### 1.2.4.2.4 Frequency Dependence

Also the C-V curve of a MOS capacitor is frequency dependent. At high frequency, beyond the Threshold voltage ( $V_{th}$ ), the minority carrier generation and recombination is not quick enough to oscillate quasi-statically with the frequency variation. Hence the capacitance saturates beyond the threshold voltage for high frequency. But if the frequency of the applied bias is low enough, the minority carrier generation can provide enough carriers to the semiconductor interface with increasing voltage. Hence the capacitance increases again in the inversion region before saturating as shown in Figure 1.2.8.

#### 1.2.4.2.5 Deep Depletion Mode

If the rate of increase of applied voltage on gate is large enough, the capacitance continue to decrease beyond the threshold voltage too. This is caused by continual increase of the depletion layer thickness beyond the threshold voltage as the minority carriers are not able to meet the increasing positive potential on the gate. This mode is known as Deep Depletion mode.

### 1.2.5 Current-Voltage Characteristics

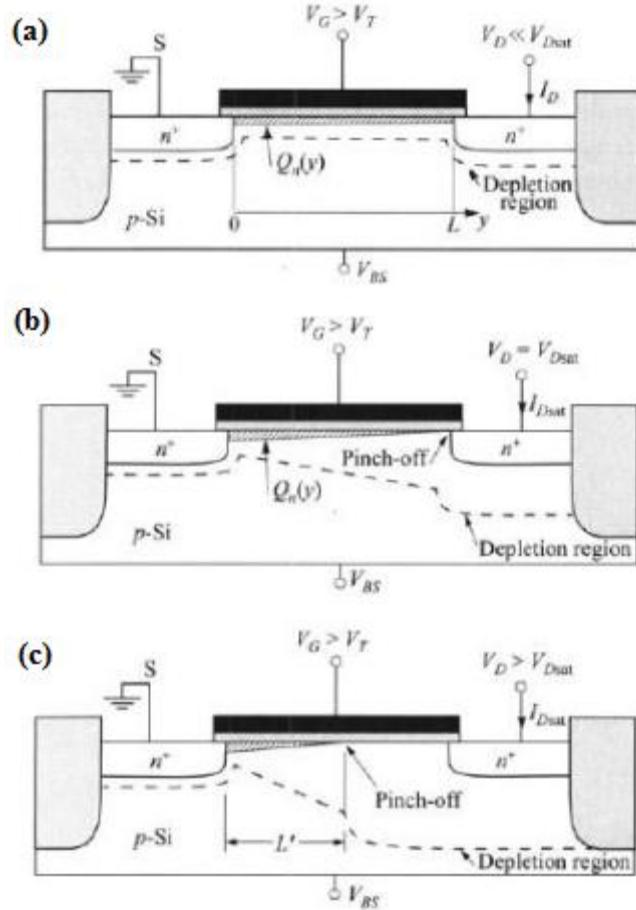

MOSFET is a four terminal Device with four terminals as Source, Drain, Gate and Substrate. For an n-channel MOSFET, when the gate voltage ( $V_G$ ) exceeds threshold voltage ( $V_T$ ), an inversion layer of electrons is formed at the semiconductor surface forming a conducting channel in between source and drain. When a positive drain voltage is applied in this condition, the MOSFET starts to conduct. Source and Substrate terminals are usually shorted to ground potential. The conduction of MOSFET can be divided into three regimes, e.g. linear regime, onset of saturation regime and strong saturation regime.

- **Linear regime ( $V_G > V_T$  and  $V_D < V_G - V_T$ ):**

In this region a conducting channel of electron is formed for gate voltages higher than the threshold voltage. The channel formed behaves like a resistor and with increasing positive voltage applied to the drain, it starts conducting. The drain current increases linearly with drain voltage in this regime, so it is called linear region in the output characteristics of a transistor. However, the voltage drop as well as the depletion region in the source and drain increases with increase in drain voltage and weakens the inversion layer as shown in Figure 1.2.9(a).

- **Onset of Saturation regime ( $V_G > V_T$  and  $V_D = V_G - V_T$ ):**

With increase in drain voltage, the depletion width increases in drain and source region and progressively narrows the channel width. Because of the voltage drop, the gate voltage varies from  $V_G$  at source to  $V_G - V_D$  at drain. When  $V_G - V_D = V_T$ , then the channel near drain becomes narrowest and the pinch-off is said to occur as shown in Figure 1.2.9 (b).

- **Strong Saturation regime ( $V_G > V_T$  and  $V_D > V_G - V_T$ ):**

With further increase in drain voltage, the pinch-off point moves closer and closer to the source-end and the pinch off region widens. This region has high resistance and little carriers. The electrons are attracted from the source region into the channel and are drifted across the pinch off region by strong longitudinal electric field present in the region as shown in Figure 1.2.9 (c). In this region, a change in drain voltage, doesn't cause a significant increase in drain current, hence it is called the saturation regime.

**Figure 1.2.9. NMOSFET in various operating conditions, (a) linear regime, (b) onset of saturation and (c) Strong saturation regime [1].**

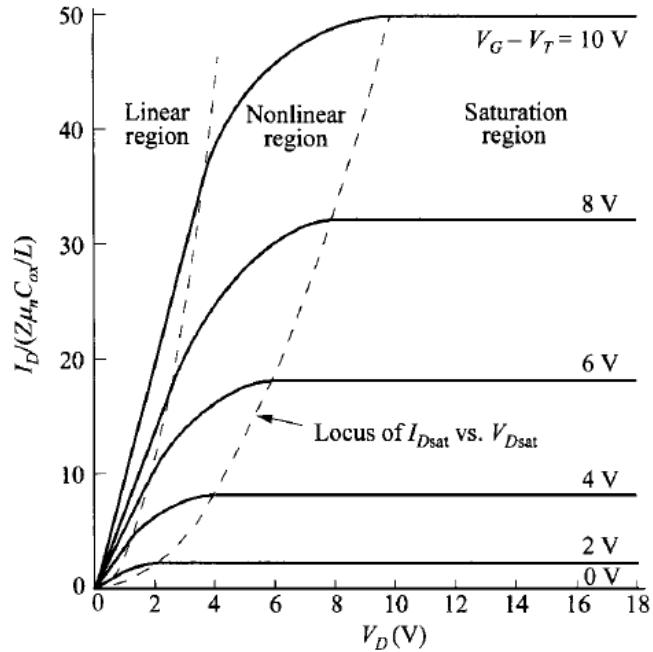

### 1.2.5.1 Output Characteristics ( $I_D$ vs. $V_D$ ):

An ideal  $I_D$  vs.  $V_D$  characteristics of n-channel MOSFET is as shown in figure below. The channel contains mobile charge carriers whose charge is given by,

$$Q_n = -C_i(V_G - V_T - V_x)$$

Where,  $V_G$  is the applied gate voltage,  $V_D$  is the applied drain voltage and  $V_x$  is the voltage at a distance  $x$  from the source. The conductance of a differential element  $dx$  in channel is given by,  $\mu_n Q_n(x) Z dx$ , where  $\mu_n$  is the surface mobility,  $Z$  is the channel width. Drain current is obtained by integrating the conductance over the channel given by,

$$\int_0^L I_D dx = \int_0^{V_D} \mu_n Z |Q_n| dV_x$$

Which gives the expression of resulting drain current to be,

$$I_D = \frac{\mu_n Z C_i}{L} \left[ (V_G - V_T) V_D - \frac{V_D^2}{2} \right]$$

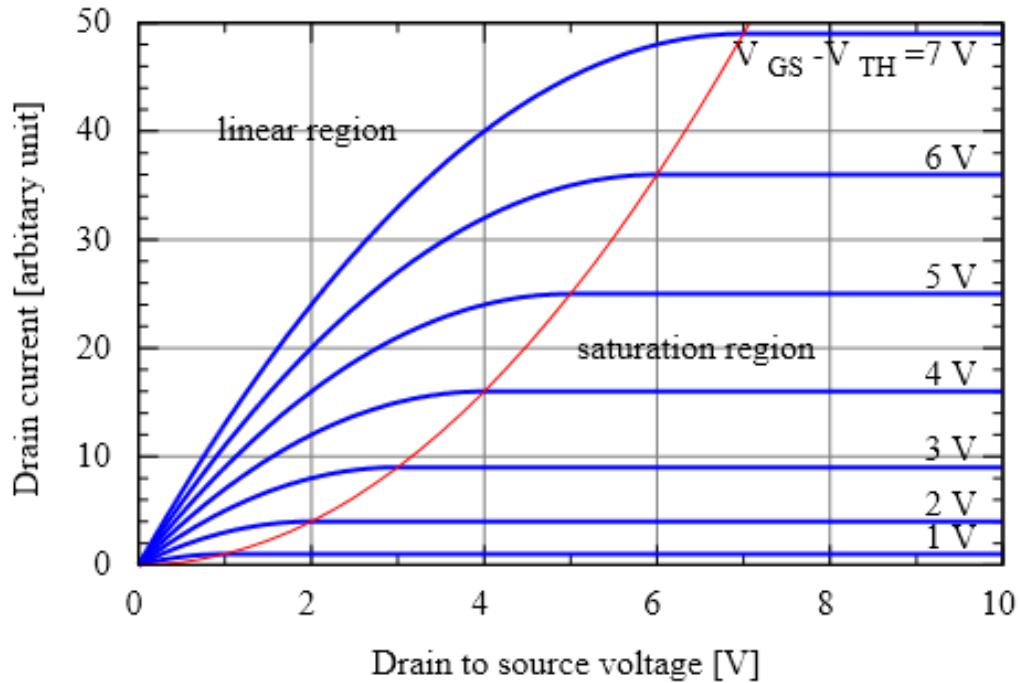

**Figure 1.2.10 Ideal  $I_D$ - $V_D$  characteristics of an NMOSFET with dotted lines separating the linear region, non-linear region and saturation region from each other [1].**

The conductance can be of two types-

- Channel Conductance ( $g_d$ ): It is the rate of change of drain current with respect to drain voltage at constant gate voltage. It can be determined from the slope of the output ( $I_D$ - $V_D$ ) characteristics. It is given by:

$$g_d = \left| \frac{\partial I_D}{\partial V_D} \right|_{V_G}$$

- Transconductance ( $g_m$ ): It is the rate of change of drain current with respect to gate voltage at constant drain voltage. It can be determined from the slope of transfer ( $I_D$ - $V_G$ ) characteristics. It is given by:

$$g_m = \left| \frac{\partial I_D}{\partial V_G} \right|_{V_D}$$

$I_D$  -  $V_D$  relationship in different regions of output characteristics can be given by:

1. Linear region:

The relationship is linear in this region at  $V_D \ll V_G - V_T$ , given by:

$$I_D = \frac{\mu_n Z C_i}{L} \left[ (V_G - V_T)V_D - \frac{V_D^2}{2} \right]$$

and transconductances are given by:

$$g_d = \left| \frac{\partial I_D}{\partial V_D} \right|_{V_G} \cong \frac{\mu_n Z C_i}{L} (V_G - V_T)$$

$$g_m = \left| \frac{\partial I_D}{\partial V_G} \right|_{V_D} \cong \frac{\mu_n Z C_i}{L} V_D$$

2. Onset of Saturation region:

The relationship in this region where  $V_{D(sat)} = V_G - V_T$

$$I_{D(sat.)} \cong \frac{\mu_p Z C_i}{2L} (V_G - V_T)^2 = \frac{\mu_p Z C_i}{2L} (V_{D(sat.)})^2$$

and transconductances are given by:

$$g_d = \left| \frac{\partial I_D}{\partial V_D} \right|_{V_G} \cong 0$$

$$g_m = \left| \frac{\partial I_D}{\partial V_G} \right|_{V_D} \cong \frac{\mu_n Z C_i}{L} (V_G - V_T)$$

### 1.2.5.2 Transfer Characteristics

The transfer characteristics of a device are expressed as a curve of drain current as a function of gate voltage, while drain voltage is held constant. There are two characteristic regions of the transfer characteristics curve, the linear region and the saturation region. In the linear region the drain current changes linearly with the gate voltage. The linear threshold voltage is found through finding a linear fit for the linear region. The x-intercept of the fit is the linear region threshold voltage, and the slope of the fit is the transconductance of the device.

As the gate voltage is increased the system enters the saturation region and the transfer characteristic curve begins to show parabolic behavior. It is helpful to plot the square root of the drain current as a function of gate voltage to examine this region. Taking a linear fit of this region in the square root of drain current plot allows us to extract the threshold voltage for the saturation region.

### 1.2.6 Non-ideal MOSFET

Theory is very informative on how a device can be expected to behave, but it is very difficult to fabricate a device that shows actual ideal behavior. There are multiple different effects that contribute to non-ideal behavior in a MOSFET device.

#### Work Function Difference:

In the ideal case we assumed that the work function of the metal gate was identical to the work function of the silicon dioxide. This is not going to be true in any real device. The difference in work functions will cause a shift in the threshold voltage, making it non-ideal.

#### Mobile Charge:

Highly diffusive species, such as  $\text{Na}^+$  and  $\text{K}^+$ , are likely to be present in the oxide as contaminants introduced during fabrication. These contaminants change the threshold voltage off the device.

#### Fixed Charge:

The production of the oxide layer usually leaves excess ionic silicon at the interface between the silicon and the oxide. These 'dangling bonds' are usually formed when the oxidation process is ended abruptly. These fixed charges cause a shift in the flatband voltage of the device.

### 1.2.7 Additional Effects in MOSFETs

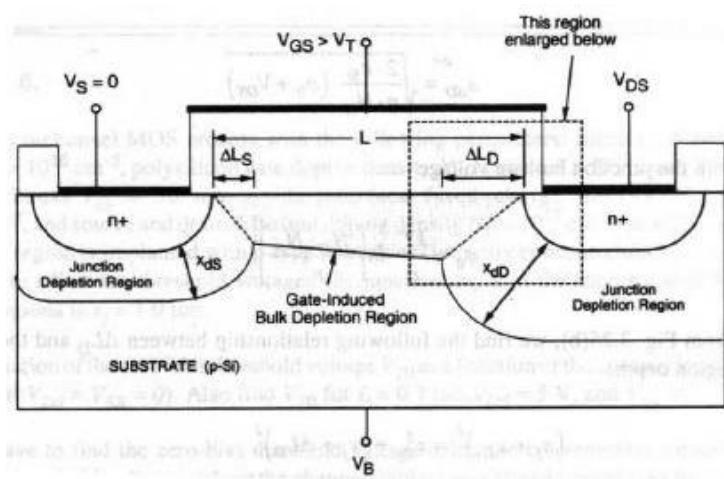

#### 1.2.7.1 Short channel effect

Short –channel effect is a consequence of scaling down MOSFET sizes. When a FET is small enough such that the channel length is the same order of magnitude as the depletion-layer widths of the source and drain junction. The short channel effect modifies the threshold voltage thereby altering the performance of the FETs.

The short channel effect can be attributed to 2 physical causes; the limitation due to the electron drift characteristics in the channel and the modification of the threshold voltage that occurs from shortening the channel length. The following are the 5 short channel effects that have been observed to occur

- Drain-induced barrier lowering and punchthrough

- Surface scattering

- Velocity saturation

- Impact ionization

- Hot electrons

**Figure 1.2.11 Simplified geometry of a short channel FET**

### 1.2.7.2 Drain -Induced barrier lowering

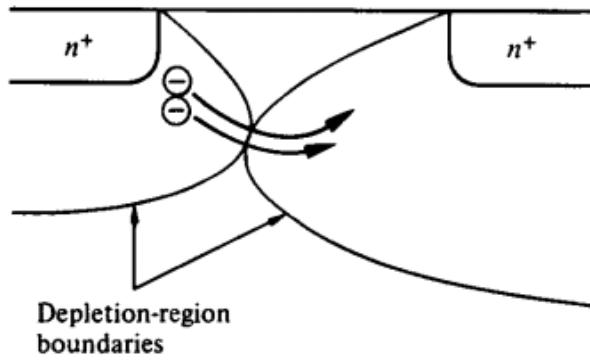

This is one of the consequences of short channel effect. When the channel is not long enough, the depletion layers of the drain and the source merge and punchthrough occurs. Current can only flow when an inversion layer has been created by applying bias at the gate. If this gate bias is not large enough to invert the surface, the electrons (or holes) form a barrier that blocks flow in either direction. This can be corrected by increasing the gate voltage. But in small channel devices, drain to source bias also affects this barrier, therefore when the drain voltage is in-

creased it leads to the Drain-Induced barrier lowering effect. This means the threshold voltages can be reached at lower gate voltages because the drain voltage is contributing to the threshold voltage value, which it normally shouldn't.

**Figure 1.2.12 Punchthrough between source and drain.**

The solution of this is to make shallower junctions, thinner oxides or longer channels.

### 1.2.7.3 Substrate bias effect

The substrate bias effect also known as the body effect is the modification of device threshold voltage through the application of bias on the substrate (body) of the device. The depletion layer is affected by the voltage difference between the source and the bulk (body). The change in threshold voltage is given by

$$\Delta V_T = \frac{\sqrt{2\varepsilon_S q N_a}}{C_{ox}} (\sqrt{2\phi_F + V_{SB}}) - \sqrt{2\phi_F}$$

where  $V_{SB}$  is the bulk-to-source voltage. A change in  $V_{SB}$  would therefore cause a corresponding shift in the threshold voltage. The body is sometimes referred to as “second gate” because of the effect it has on the threshold voltage and how it can turn on or off the transistor. The way to

combat this is to set a fixed body bias voltage and that way the body voltage is always constant and is no influenced by device doping

### 1.3 Basic Processing Steps for MOSFETs

Fabrication of devices includes basic processes like Photolithography, Ion implantation, Oxidation, Etching, Diffusion, Material Deposition, and Metallization. Due to increasingly small device dimensions, keeping impurities out of the fabrication process is one of the driving forces behind processing innovation and techniques. Majority, if not all are carried out in pristine contaminant free environment, known as clean rooms. The one where the processing of these wafers took place was a 100 rating clean room which is the number of 0.5um impurities per cubic feet. The different scales of clean room can be seen below in Table 1.3.1. The 1 rating clean- room is a little difficult to measure however.

**Table 1.3.1 Clean room rating by air purity**

| Rating | Number of 0.5um particles per cubic feet | Number of 5-um particles per cubic feet |

|--------|------------------------------------------|-----------------------------------------|

| 10,000 | 10000                                    | 65                                      |

| 1000   | 1000                                     | 6.5                                     |

| 100    | 100                                      | 0.65                                    |

| 10     | 10                                       | 0.065                                   |

| 1      | 1                                        | 0.0065                                  |

In industry, most of the processes are automated, and devices orders of magnitude smaller, smallest consumer ready transistor size is Intel's 22nm technology, are being manufactured. The importance of precision and even less contamination is worth millions. Wafer uniformity is important and contaminants affect device performance in unpredictable ways. Impurities can affect critical parameters like threshold voltage ( $V_{th}$ ) which needs to be the same or have minimal percentage error, if they are to be used in the same top level circuitries.

Sources of contamination usually include, organic materials from humans, which can introduce extra charges to the devices, thereby affecting parameter like electron/hole mobility. The

processes listed above would be discussed in detail below. These are the key steps required to make a functional MOSFET and through mask manipulation other structures like transistors, capacitors, van der pauw structure, Kelvin structures are made. These are important in the characterization of the MOSFETs.

### **1.3.1 Wafer Cleaning:**

Wafer cleaning is usually done using the RCA clean. This is important for the removal of organic contaminants, ionic contaminants, and in some cases thin oxide film.

RCA Clean:

The first step is to remove all the organic materials by dipping the wafers in a heated ammonium hydroxide (NH<sub>4</sub>OH), Hydrogen Peroxide (H<sub>2</sub>O<sub>2</sub>), and Deionized (DI) water solution using a ratio of 1:1:5 respectively. A pre-solvent clean, using acetone can be done, but not necessary. During this step the solution removes organic residues and also oxidizes the silicon and leaves a thin oxide layer on the surface of the wafer.

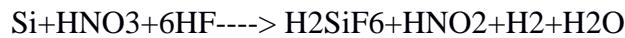

The next step is a quick dip in a HF and water solution with ratio of 1:50 respectively at 25°C to remove the thin oxide layer that was caused by the previous step. This is done for a very short time because the solution reacts quickly. Safety precaution must also be taken by wearing protective gear due to the dangerous nature of the chemicals being handled.

The last step is done to remove ionic contaminants which may have been introduced in the previous steps. The wafer is dipped in a solution of Hydrochloric acid (HCl), H<sub>2</sub>O<sub>2</sub> and DI water using a ratio of 1:1:5, respectively.

The wafer is cleaned using a quick dump rinser (QDR) using deionized water, after every step to prevent the chemicals used in that step from reacting with the ones in subsequent steps. Finally it is dried and cleaned because water can easily attract floating particulates if left on the surface.

### **Piranha Solution:**

Another cleaning method is piranha etch, which contains a mixture of sulfuric acid (H<sub>2</sub>SO<sub>4</sub>) and H<sub>2</sub>O<sub>2</sub>. This is a strong oxidizing agent however, and leads to formation of oxide on the wafer surface.

The solution must be handled extra cautiously because it is an exothermic reaction and releases heat of over 100°C. This high temperature may cause vigorous boiling and splashing of extremely toxic solution. It must be allowed to cool reasonably before applying any heat.

This method is mostly used to clean photoresist residue from the silicon wafers. The equation below is the mechanism of operation of this solution. The product, H<sub>2</sub>SO<sub>5</sub> (Caro's acid) is the key component that vigorously dehydrates the residues in the manner of which piranhas feed; hence the name Piranha solution.

### 1.3.2 Thermal oxidation:

The ability of silicon to form  $\text{SiO}_2$  is the major reason why Si is the dominant material used for the fabrication of MOSFETs. The oxide serves as a diffusion barrier during impurity diffusions, protection for the p-n junctions formed due to the presence of source and drain wells in the substrate, insulating film to separate different levels of devices, as isolation structure, and passivation layer.

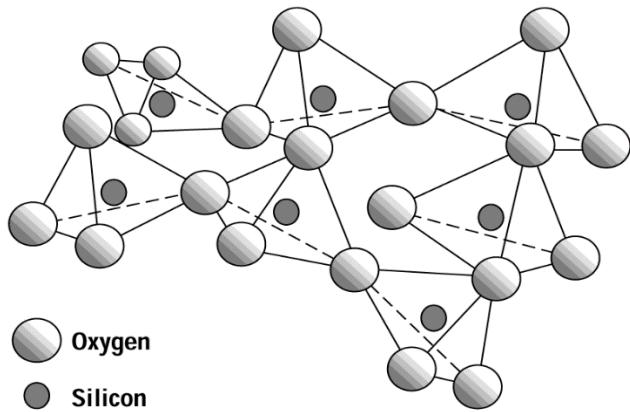

Two types of oxides can be formed based on the uniformity of the atomic configuration. Fused silica is amorphous  $\text{SiO}_2$  which is the oxide we are interested in based on the arrangement of atoms in the molecule. The other type of  $\text{SiO}_2$  that can be formed is known as Quartz.

**Figure 1.3.1 Physical structure of  $\text{SiO}_2$**

Oxidation can be done either by using pure oxygen (dry oxidation), or water vapor (wet oxidation). They both have their pros and cons and depending on the application of the oxide either or both can be used to form  $\text{SiO}_2$ . Oxidation is done at really high temperatures, between 700 – 1300 oC and is therefore referred to as Thermal oxidation. Dry oxidation is slower but produces lower quality oxide, whereas wet oxidation is faster but produces poorer quality oxide. Wet oxidation is faster because the solid solubility of (OH) in  $\text{SiO}_2$  surface is several orders of magnitude higher. The mechanism for dry and wet oxidation can be seen below:

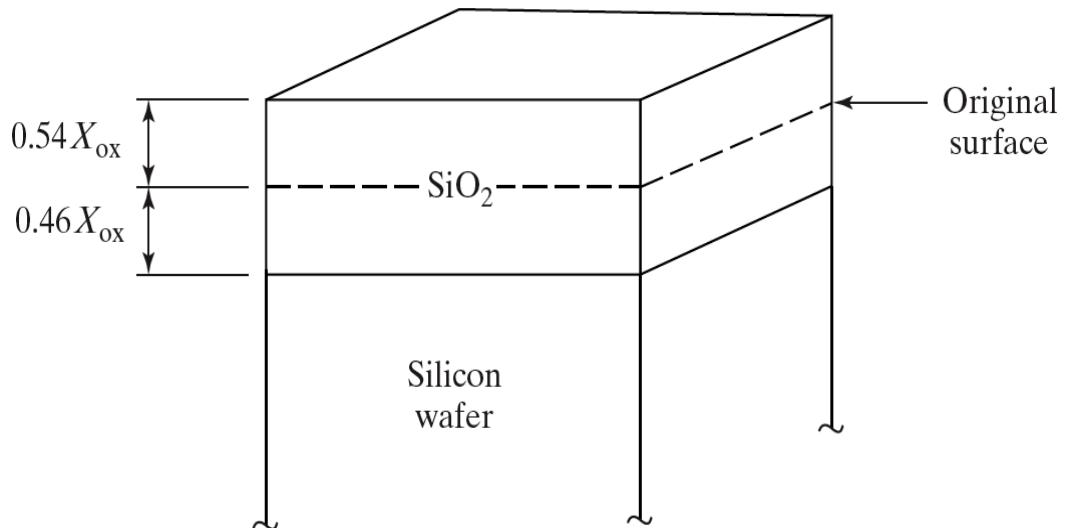

The thickness of oxide produced during oxidation needs to be anticipated and accounted for when determining the thickness of the substrate. This is because the oxide eats some of the silicon wafer to produce the oxide, and that's usually around 46% of the thickness of the final oxide layer.

**Figure 1.3.2 Final Si surface after oxidation**

The oxidation process takes longer with more time because the diffusing species need to travel through increasing thickness of the oxide layer to reach the silicon and form  $\text{SiO}_2$ .

#### Reaction Kinetics:

The final thickness of oxides grown can be calculated by knowing the initial concentration of oxygen at the Si-SiO<sub>2</sub> interface, conc. in the reacting species and the flux (flow of oxygen molecules). The equation derived from these is

$$X_o = 0.5A((1+4 B/A^2 (t+ \tau))^0.5 - 1). \quad T = X_o^2/B + X_o/(B/A) - \tau$$

$$\tau = X_i^2/B + X_i/(B/A).$$

Where  $X_o$  = final oxide thickness,  $D$  = diffusion coefficient,  $N$  = concentration of oxygen,  $X_i$  = initial oxide thickness  $\tau$  = initial time required to grow initial oxide,  $t$  = time elapsed.  $A$  and  $B$  are constants that vary with temperature,  $D$ ,  $N$ , and pressure.  $B/A$  is called the linear rate constant and  $B$  is called the parabolic rate of oxygen through the oxide.  $B/A$  is more important for small oxide thicknesses and the thickness increases with time linearly, hence linear rate constant. The longer the time, however the thickness increases with the square root of time, hence parabolic rate constant. If the time is long enough, the thickness ( $X_o$ ) can be estimated by  $X_o^2 = Bt$ .

**Table 1.3.2 Linear and Parabolic rate constants for dry and wet oxidation**

TABLE 3.1 Values for Coefficient  $D_0$  and Activation Energy  $E_A$  for Wet and Dry Oxygen\*

| Wet $O_2$ ( $X_i = 0$ nm) |                                   | Dry $O_2$ ( $X_i = 25$ nm) |                                   |

|---------------------------|-----------------------------------|----------------------------|-----------------------------------|

| $D_0$                     | $E_A$                             | $D_0$                      | $E_A$                             |

| <100> Silicon             |                                   |                            |                                   |

| Linear (B/A)              | $9.70 \times 10^7 \mu\text{m/hr}$ | 2.05 eV                    | $3.71 \times 10^6 \mu\text{m/hr}$ |

| Parabolic (B)             | $386 \mu\text{m}^2/\text{hr}$     | 0.78 eV                    | $772 \mu\text{m}^2/\text{hr}$     |